MPF 2008: 混合架构主宰消费类领域

同构架构已经兑现了其承诺:有效的低功耗、灵活性以及准备好应对任何新的工作负荷,加上在互联网上升级消费电子系统的好处。然而,在日本举行的2008年微处理器论坛(MPF)上,为期两天的日程上填满了24个演讲,其中,两个是主题演讲,除了软件工具之外,只有一个演讲可能声称描述同构架构设计。

本文引用地址:https://www.eepw.com.cn/article/89405.htm各个公司提交的异构(heterogeneous)设计存在差异,但是,它们有一点是共同点:它们并不是由节省功率而展示的高度并行的同构架构。更为精确地说,把在一颗芯片上的四颗处理器视为构成一种高度并行同构架构是不公平的。然而,即使一颗芯片宽大地把它们包含在一类中,在2008年日本MPF上,所展示的大多数四引擎同核实现均采用与硬线连接的加速器接口挂钩来实现的,而不是增加更多的相同的ISA核,以便不需要特殊目的引擎就完成任务。

丰富的配置

根据处理通用目的控制工作负载所采用的配置以及所实现的针对特定应用的加速方法,在2008日本MPF上所展示的架构可以分为几类。

在混合架构设计中,控制引擎由作为一个多核处理器工作的若干通用目的内核实现或仅仅由一个内核实现。引擎可接受的功耗取决于执行通用目的应用以及控制不同的音视频编解码器所需要的性能。一般来说,处理器必须有效率,但是,所需要的效率范围进一步依赖于功率的可用性。在起居室中的多媒体应用的要求可能更为宽松,而安装在汽车中的系统将期待更佳的效率。蜂窝电话和其它电池供电的手持设备将被设计为消耗最低的功率。

加速器的设计可以采用几类实现方案,从采用定制指令集架构(ISA)的内核、参数受控的灵活状态机到固定程序硬件连线的实现。根据在控制处理器以及加速器之间是否需要去掉存储器访问,可能要或不要提供本地存储器。

架构设计的分配

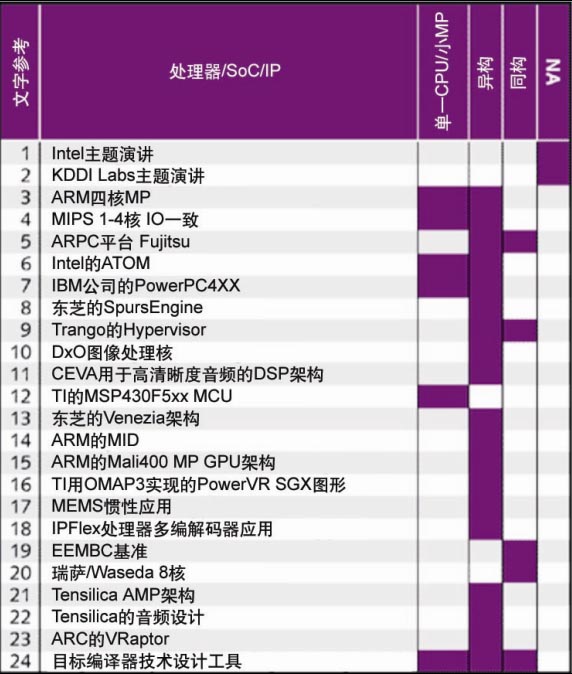

架构配置的分配结果是不言而喻的(表1)。在表1中,“Text Reference”一列指的是对表中列出的有限陈述的简短描述;这些陈述由描述每一个陈述的加括弧的数字来识别。

表1:对于在器件的实现中所采用的架构类别来说,通过表中的各栏可以识别在2008日本MPF上展示的最佳匹配的处理器/SoC/IP。处理器的标题为缩写。参考数字可以被用来查找陈述的简短描述。软件已经被包含以实现完备性,但是并不总是显示硬件的存在。

为了公平起见,我们已经省略了两个可能显示异构芯片的主题演讲,但是,并不是如此明确。会议的背景集中在娱乐之处,并且暗指需要不同的架构配置,这些配置由英特尔公司的副总裁、数字娱乐组的Ton Steenman以及KDDI Labs公司的执行总监Hiroki Horiuchi做了适当的设置。他们的演讲在描述不久将受到欢迎的连接固定和移动设备(Ton Steenman) [1]的世界上相互补充,而网络和无线电意味着[2]保持它们的工作(Hiroki Horiuchi)。我们还省略了四个重点放在软件的演讲;我们发现在18个新的设计中,17个不是同构设计。我们还发现,所介绍的大多数软件工具重点放在基准上,并提供对同构架构的并行支持。

从统计上看,采用24个演讲作为样本就得出关于一个覆盖全球人口的平均数的结论是不准确的,除非已知这个样本代表可靠的覆盖率。考虑那些已经在2008日本MPF上做演讲的公司,我们能够假设它们大部分代表了IP、处理器以及复杂SoC设计的领导者。如上所述,这一统计数字说明,我们试图解释的状况出自如此高度偏向有利于异构架构的样本。

在大批量销售的消费娱乐芯片中,有三个较之于其它应用更为重要的参数:(1) 流片投资;(2) 在并行化编译器上缺乏突破;(3) 进展缓慢的音视频标准。

根据作者的感觉,表2示出了对实现技术的、总是有帮助但可能引起争议的定性比较。数字代表分析师的定性估计而不是精确的数据。数字越小则越好。

表2:该表格根据作者的感觉对各种实现技术进行了定性比较。数字越小越好。在价格敏感的应用中,并行同构架构表现不那么好。异构架构将需要重新说明,只要新的编解码器看起来不能由控制加强的內核执行的话。然而,这些将在每几代出现一次,并且大多数的硬连线或定制ISA单元仍将是可重用的。

并行同构实现根据整个比较参数被给予一个平均打分,因为这些实现在灵活性、降低开发风险、远程诊断或升级上较之于异构架构更好。然而,它们在流片投资以及—更为重要的是—软件工具上落后于其它架构。

最佳打分仍然看起来属于单核或四核、“高频”实现。这个配置将继续被使用,只要运行应用所需要的性能能够允许芯片的功耗被保持在控制之中。

对于批量销售来说,两个异构是最佳的。流片投资低,使得裸片价格在消费应用中有竞争力。开发风险高,因为它意味着要采用ASIC设计且所得到的芯片具有较低的编程灵活性,然而,如果它导致非常高的营业收入就非常值得投资。附加的优势是在定制ISA和硬线编解码器上:标准进化缓慢。设计工程师能够重用定制ISA以及在许多芯片中的硬线加速器。

芯片和内核被随意连接至加速器

相当多的演讲提供了具有或不具有加速器的、采用一个小型MP群的选择权。由ARM公司高级编程经理John Goodacre讲述的四核MP配置采用了该公司最新的Cortex-A9,它可能被认为是一种混合架构,因为它通过其NEON协处理器提供DSP处理。然而,ARM还实现了一种连接,通过它多个处理器群能够与定制设计的加速器配合工作。MIPS技术公司的高级工程师Tom Berg介绍了在多线程处理器中的IO一致性,解决了一种类似的MP配置。它能够在SoC中采用该公司的1~4MP核,从而把通用目的处理与调谐器、解码器以及图形加速器一起集成进混合架构的实现之中。

Fujitsu Laboratories的演讲由Processing LSI Development Group总监Atsuhiro Suga提供。Atsuhiro Suga在2007年日本MPF上就因他的软件演讲而知名。在那时候,他介绍了一种被用于在多个处理器之间分配任务的异步远程程序调用(ARPC)的应用,它与那些不必在相同的ISA上实现的引擎集合起来(见MPR 8/13/07-01, “Fujitsu Calls Asynchronously”一文)。Suga的新演讲[5]描述了增加的一种硬件状态机,以替代可能相同的处理器之一,迄今为止,这项任务利用有待状态机处理的工作负荷的线程进行调度。

英特尔公司的首席架构师Belli Kuttanna介绍了它的Atom芯片,不久前,该公司宣布它已经进入复杂的采用多种设计的SoC市场,其中一些是基于双线程Atom架构。一个这样的SoC设计把计算复杂体与媒体加速器结合起来,实现图形、音视频以及显示器引擎,还允许第三方知识产权被连接起来。Atom芯片连接可以随意接上加速器的处理器组,它们是完全或部分可编程的。

IBM公司的顾问研发工程师Masahiro Murakami讲述了IBM的PowerPC4xx SoC平台[7],描述了允许把用户定制逻辑连接至PowerPC内核以创造多核异构设计的接口装置。这种至PowerPC内核的连接性是通过把连接内核的本地总线桥接至AHB总线来实现的。在以前的单一或异构配置的PowerPC设计中,如Cell BE,可以成为高度集成的SoC的控制器。

异构架构

东芝负责蜂窝项目的项目带头人Yoshio Masubuchi演讲了该公司的SpursEngine [8],并且是该公司领导该芯片开发的逻辑选择。 SpursEngine的设计结合了来自8-SPE Cell BE的四个增效处理器单元(SPE),加上支持不同视频编解码器的硬件加速器。

Trango Japan公司的领导Tom Kobayashi讲述了面向DRM的安全执行环境的实现。Kobayashi描述了Trango的系统管理程序的安全软件域的应用。Trango的系统管理程序在一个或多个操作系统以及基础硬件之间形成一种抽象层。它能够把一个或多个处理器分为独立安全和针对应用执行的域。处理器本身可以是相同的或者可以作为混合架构被实现。

DxO Labs的首席运营官Bruno Liege讲述了一种可配置、可编程、面向像素的、高质量、高性能、可授权的IP架构[10],它被设计为一种把窄数据路径、12-bit标量引擎级与宽向量处理级相结合的加速器。多个ALU结构由采用ARM的AHB总线的内核中的标量逻辑进行控制。

CEVA公司的核心架构总监Michael Boukaya的演讲与在消费娱乐中缺乏成功的高度并行引擎的许多其它实现相比,更为让人大开眼界。CEVA的32-bit DSP单一引擎所获得的性能是通过在DSP内核上采用高频,加上用于专用函数如FFT和维特比的加速器来实现的。

德州仪器(TI)的超低功耗MSP430F5xx MCU家族[12]由MSP430 MCU首席架构师Horst Diewald讲述,它利用在性能上的提升进一步提供超低功耗控制。Horst描述了通过硬件和软件相结合来管理处理器,以实现诸如远程抄表、对用于安全目的的气体泄漏的检测、个人医疗以及能量收集等功能所要求的低功耗数字。新家族的芯片增加了一体化外设,如射频、加密以及至MSP430平台的LCD接口。

东芝的首席专家Takashi Miyamori介绍的Venezia架构[13]能够利用由用户选择的主CPU—如ARM或MIPS—实现一种控制资源,加上由不同的处理器—如控制和线程的分派所需要的—实现的加速Venezia引擎,一个调度器,以及一些媒体处理引擎。

ARM公司的研发组咨询工程师Nigel Paver描述了移动互联网设备(MID)[14]可配备内部处理资源的途径。根据Paver的介绍,高性能的MID能够利用由高端摄像机图像处理器、三维图形引擎、高清视频编解码加速器、TrustZone安全性以及包含GPS基带功能的、支持的Cortex Aclass内核来实现的异构架构。稍廉价的较低性能MID还可以由TrustZone实现加密。MID可以由ARM11内核控制。它可以配合较低性能的摄像机、非高清视频编解码器、不太先进的三维图形以及一体化的无线基带。

此外,ARM公司的高级产品经理Chris Porthouse讲述了Mali400 MP GPU架构[15],其用途是与ARM CPU内核在同一芯片上工作。Mali-400 Vertex处理器以及多达四个片段处理器被通过本地互连连接至MaliMMU。MaliMMU被连接至一个L2高速缓冲存储器,它本身接至AXI总线。ARM公司的一部APB外设总线被用于把数据传输至Vertex和片段处理器以及至MaliMMU和L2高速缓冲存储器。

TI公司的图形软件工程师Clay D. Montgomery讲述了由OMAP3家族之一的OMAP35x应用处理器所采用的图形内核[16]。TI在OMAP3530高集成度处理器中正采用由Imagination Technologies提供的异构PowerVR SGX图形内核。该芯片还集成了一种TMS320C64x+ DSP内核,加上图形外设以及加速器。异构OMAP35x平台以Cortex-A8内核为基础。

ADI日本公司微机电技术组总监Yutaka Katano以及In-Stat技术分析师Max Baron讲述了一种泛系统的异构架构[17],采用了DSP处理器、MEMS、运算放大器以及连接至桌面的蓝牙接口。

SATO创始人Tomoyoshi与IPFlex首席技术官IPFlex介绍了一种异构架构[18],它采用大量不同的功能处理单元(PE)以及能够更加有效地处理MPEG-2/-4和H.264比特流的增强比特流处理器(BSP)。

PE和BSP单元能够被动态地重新配置以执行在前景中的各种任务,与此同时,通过从外部存储器加载下一个配置信息而在背景中设置新的任务。尽管它具有灵活性,IPFlex公司的新引擎能够执行多个编解码器的应用,这一功能在产品发布之后会加入设计中,它还能够被配置为执行针对用户的工作负荷。

同构架构

日本嵌入式微处理器基准联盟(EEMBC)的区域经理Satoshi Otsuka讲述了面向多个内核以及高度并行同构架构的基准状况。对于MPR了解的最佳情况来说,该联盟仍然就针对采用相同内核进行配置的最初套件进行最终完善。瑞萨公司提供且由日本Waseda大学开发的高性能并行化编译器所支持的一种8个CPU的多核处理器[20],被认为应该考虑为同构架构。Waseda大学的教授Hironori Kasahara以及瑞萨科技公司的部门经理Toshihiro Hattori轮流介绍了OSCAR编译器以及多核架构。

同构可配置、可扩展处理器

Tensilica公司的技术福音传道者Steve Leibson描述了可扩展配置的优点,他认为,对称多处理器(SMP)架构对于服务器不错,但是,在多媒体应用中的运行效率不高。Tensilica的方法就是采用在公司的基本Xtensa架构上实现的针对应用的ISA[21]来创建加速器。异构架构—如在爱普生打印机中所采用的—被用于描述这类加速器的应用。

Tensilica公司的Darin Petkov介绍了一种音频设计,它采用了由ISA扩展获得的应用专用处理器[22],在该公司的Xtensa LX VLIW基本引擎上构建了大约300个针对音频的指令。

ARC公司的首席技术官Nigel Topham介绍了该公司采用异构架构实现的VRaptor家族[23],其中有采用ARC 750D CPU针对工作负荷而配置的可编程加速器。该公司在控制它的流以及计算群的协调群中采用了类似的CPU,它们本身作为异构架构被实现。

Target Compiler Technologies公司的首席执行官Gert Goossens讲述了该公司的工具,它们有助于设计工程师创建针对应用的处理器(ASIP)[24]以及从零做起的编程工具。与采用所有其它的针对应用的引擎一样,一组ASIP内核可以被最优化以提供具有最少逻辑的SoC以及对工作负荷的良好分配,唯一的例外就是基本状态机或也是从零开始设计的简单的处理器,从直觉上看,在流片投资以及功耗上提供优势,而所付出的代价就是设计一种品牌新架构所需要的额外工程时间。

本文总结

与多核同构配置相比,异构架构提供有利于流片投资以及功耗的更佳折中。回顾过去可见,在流片投资、功耗以及软件创建上同构架构要变得更为舒适,设计工程师必须看到用于相同ISA内核的更多优势。

目前,同构架构的状况使之更加适合于高度数据密集的处理工作。对于家庭娱乐以及移动应用来说,在一个量产芯片的设计工程师的喜好中,同构架构仅仅高于FPGA。同构配置将在面向即将出现的应用—如专用图形、游戏和汽车视频图像识别—中获得优先权。

同构架构在低成本、大批量应用中获得竞争力以前,硬线连接以及针对应用的内核IP提供商将有机会赢得市场占有率。

评论