英特尔收购阿尔特拉,发布向GPU的宣战宣言——新FPGA

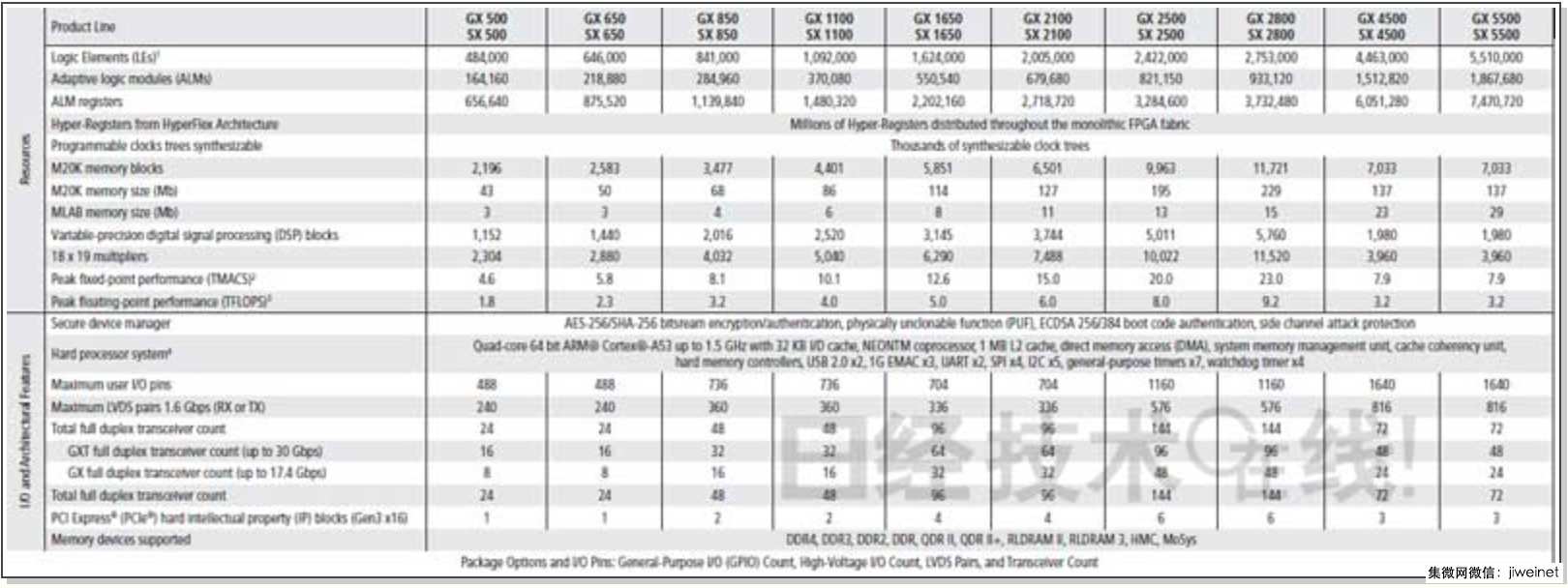

美国阿尔特拉公司(Altera)发布了预定于2015年底供应样品的高端FPGA“Stratix 10”的详情。Stratix 10由2015年6月1日(美国时间)宣布收购阿尔特拉的美国英特尔公司代工,是利用14nm工艺制造的FPGA。

本文引用地址:https://www.eepw.com.cn/article/275499.htmStratix 10虽然以前就公布了概要,但披露器件产品线等详情还是首次。预定于2015年第四季度供应样品。

图1:接受《日经电子》采访的阿尔特拉产品营销高级总监Patrick Dorsey

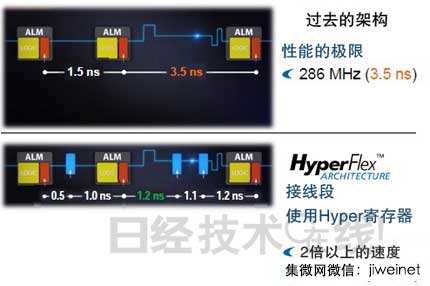

Stratix 10通过改善FPGA架构,将实现该公司以往产品“Stratix V”约2倍的性能。不仅在逻辑元件(LE)内,还在LE外部的布线部分设置几百万个寄存器,将管道细分,视用户逻辑的类型,最大工作频率可达900MHz左右。

Stratix 10与已经在供应样品的该公司的中档FPGA“Arria 10”一样,DSP硬宏支持浮点运算。最多的品种配备1.1万个以上的DSP硬宏,浮点运算性能超越美国英伟达的GPU、高达10TFLOPS。该公司的产品营销高级总监Patrick Dorsey说:“我们的产品已经可以与英伟达的GPU展开全面竞争”,显露出对GPU的竞争意识。

与赛灵思在发展方向上的差异明确

Stratix 10的特点主要有4个:(1)实现Stratix V约2倍性能的“HyperFlex架构”;(2)耗电量的削减;(3)采用英特尔的2.5D封装技术;(4)考虑到云端多租户使用的安全功能。

(1)的HyperFlex架构,是类似于微处理器的超级管道技术。是细分管道,增加段数,使其能以更高的时钟频率工作的技术。

具体来说,Stratix 10在接线段设置了专用的“Hyper寄存器”。使用该Hyper寄存器,将细分管道以提高频率。而一般的FPGA,寄存器只配置在LE内,接线段是不配置寄存器的。

图2:利用Hyper寄存器细分管道

据称,因Hyper寄存器的插入,是由编译器端自动进行的,逻辑电路设计者无需顾虑。阿尔特拉2015年5月发布的新设计工具“Quartus II”,配备了实现这一操作的功能。

按照该公司的估算,某无线通信基础设施用电路,Stratix V的最大工作频率为491MHz,而Stratix 10则为982MHz。在数据中心用的加速电路,Stratix V的最大工作频率为156MHz,而Stratix 10为452MHz。

图3:与Stratix V相比的高速化程度

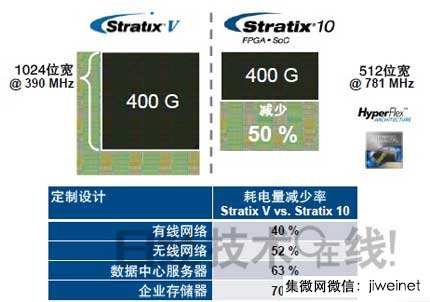

关于(2),与Stratix V相比,Stratix 10的耗电量最大可减少70%。除利用14nm工艺制造技术,降低了电源电压外,与Stratix V相比,还能以较窄的位宽实现相同的性能,据称这也有助于降低耗电量。

图4:与Stratix V相比减少的耗电量

图5:数据中心的使用示例

利用2.5D封装分离PHY,为与Xeon整合作准备?

(3)利用了代工商英特尔的2.5D封装技术“EMIB(Embedded Multi-die Interconnect Bridge)”(参阅本站报道)。

英特尔的竞争对手——美国赛灵思公司(Xilinx)也在使用2.5D封装技术,但阿尔特拉和赛灵思的使用方式完全不同。

赛灵思是把FPGA架构分成数枚芯片,用内插器连接。而阿尔特拉的战略,则是FPGA架构封装在单一芯片中,收发器电路按照不同接口,准备不同的芯片。阿尔特拉把这种芯片叫作“区块”(Tile)。

图6:区块的示意图

阿尔特拉将收发器电路作为单独芯片的理由主要有两个。一是为了方便支持今后可能面世的新一代高速接口。在支持对PCI Express Gen 4等数据速率的高速化,以及含光通信在内等新调制方式时,分芯片更容易替换,实现起来方便。

另一个是FPGA架构收纳在单一芯片中,LE之间的通信“不像赛灵思那样,无需经由不同的内插器,可以提高可靠性”(Dorsey)。赛灵思和阿尔特拉最近在片上存储器、浮点运算等许多方面,战略上的差异逐渐明确,2.5D封装的利用方法也明显不同。

阿尔特拉将收发器电路另分芯片,也可以看作是与英特尔的服务器微处理器“Xeon”整合之前的准备。英特尔在宣布收购阿尔特拉之前,一直在计划推出将Xeon与FPGA集成于同一封装的产品。通过像英伟达GPU配备的接口“NVLINK”那样,使在FPGA端容易配备可以与CPU高速连接的接口,以提高其作为加速器的利用价值。关于这一点,阿尔特拉的Dorsey表示“无可奉告”。

立足云端使用,FPGA终将实现多租户化

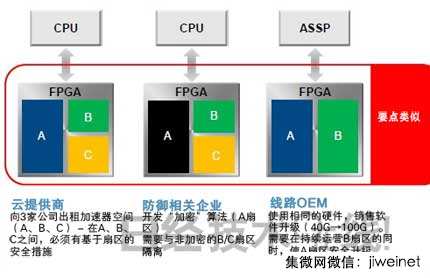

关于(4),Stratix 10加入了用来防范非法访问、防范篡改等的“安全设备管理器(SDM)”技术。在芯片内设置约15~150个扇区并予以隔离,使扇区可以单独配置和认证。

作为扇区的使用示例,阿尔特拉举出了防御设备中加密算法的隐藏、无线通信基础设施设备中特定电路的更新(在持续使用特定电路的同时,更新其他部分的电路)等。在该公司列举的示例中,最有特点的当属云服务的例子。

具体来说,就是云服务运营商在自己的基础设施中采用FPGA,把单一FPGA器件分割为多个扇区,出租给多位客户的使用形态。

这就像是在云计算领域,多家用户企业共用同一系统的“多租户”。可以说象征了“重视数据中心用途”这一阿尔特拉的现行发展方向。

图7:将单一FPGA分割使用的“扇区”使用示例

最左侧的云端“多租户”使用象征着阿尔特拉如今的发展方向

美国微软计划于2015年下半年,将为本公司数据中心大量引进FPGA,用来提高搜索引擎的速度,提供基于深度学习(CNN)的图像识别。

估计微软也在考虑把引进的大量FPGA,经由该公司的云服务“Azure”出租给客户。Stratix 10规模最大的品种配备550万个LE。达到如此规模后,在单一FPGA中划分区域,提供给多个应用、多家企业共用的利用形式便成为了可能。

PUF电路为Intrinsic ID制造

Stratix 10为加强防篡改性、加密密钥等,在高端FPGA中首次配备了PUF(physical unclonable function)电路。PUF电路是利用半导体制造误差造成的微小个体差异,生成芯片固有ID的技术。采用的PUF电路为荷兰Intrinsic ID公司制造。

配备PUF的FPGA此前美国美高森美公司(Microsemi)曾推出过,“在赛灵思和阿尔特拉的高端FPGA中配备,估计Stratix 10还是第一个”(Dorsey)。

ARM内核也实现64位化

Stratix 10与以往产品一样,也将准备配备ARM内核的“Stratix 10 SoC”。阿尔特拉的FPGA过去一直配备32位ARM内核,Stratix 10 SoC将配备64位四核“Cortex-A53”。最大工作频率为1.5GHz。(记者:进藤智则,日经Robotics)

图8:Stratix 10的品种一览

fpga相关文章:fpga是什么

评论