基于SDRAM芯片立体封装大容量的应用

SDRAM即同步动态随机存储器(Synchronous Dynamic Random Access Memory)。由于其大容量、价格优廉、无需等待时间等优点在早期的PC机种得到了广泛的应用。不同于其他的FLASH、SRAM和MRAM等存储器,SDRAM需要同步时钟,并且每隔一段时间需要刷新,否则数据将丢失。由于其功能强大、时序复杂,往往给应用者带来极大地困难。本应用案例基于珠海欧比特控制工程股份有限公司的立体封装大容量VDSD3G48芯片,介绍了对应的SDRAM控制器在FPGA上的实现,探讨其使用方法。

本文引用地址:https://www.eepw.com.cn/article/248242.htm1、VDSD3G48芯片介绍

VDSD3G48是一款容量3072M bits SDRAM 。它采用先进的立体封装技术,由六片容量为8M×16×4banks的基片堆叠而成,组成了容量为32M×48×2的48位宽的数据接口存储器。六片基片都有一个独立的片选信号,通过两组片选信号#CS0、#CS2、#CS4和#CS1、#CS3、#CS5可选择具有48位宽的不同的存储阵列。另外,通过六个片选信号和配合DQMH和LDQL信号可有选择的选择哪片基片工作和选择输出每片基片16位的高低8位,组成8、16、32、48位宽的存储器。通过应用了立体封装的技术缩短了互连导线,从而降低了寄生效应,使得器件具有高性能、高可靠、长寿命、大容量等的性能特点。

1.1 芯片的内部功能结构和外部引脚

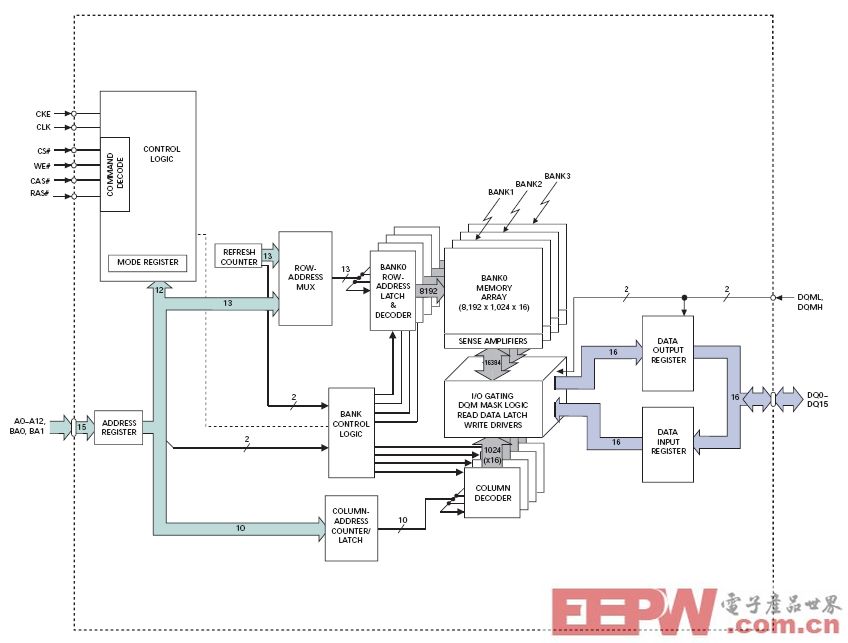

图1是立体封装的大容量芯片VDSD3G48中每一片基片的内部结构和功能框图,由MEMORY存储阵列、控制逻辑(包括指令译码和模式寄存器等)、列地址译码器、列地址锁存器、bank控制逻辑、行地址数据选择器、bank行地址锁存器、刷新定时器、读数据锁存和屏蔽和输出数据寄存器等部分组成。

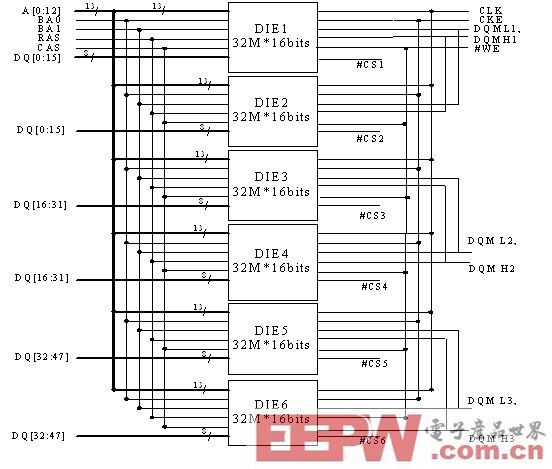

图2是立体封装的大容量存储芯片VDSD3G48的内部结构和功能框图,其中A[0:12]为地址线,BA0、BA1是banks选择信号、CLK是时钟输入信号,#CS0-#CS5是六片基片DIE1-DIE6的芯片片选信号,CKE、RAS、CAS、WE 是控制信号,DQ[0:47]是芯片的数据线,其中数据线DQ[0:15]为DIE1、DIE2的数据线,数据线DQ[16:31]为DIE3、 DIE4的数据线,数据线DQ[32:47]为DIE4、DIE5数据线,DQMH0 、DQMH1、DQMH2、DQMH3 、DQMH4、DQMH5和DQML0 、DQML1、DQML2、DQML3 、DQML4、DQML5分别为DIE1-DIE6的高低8位的输出屏蔽信号。

图1 VDSD3G48中基片的的内部功能结构框图

图2 VDSD3G48的功能总结构框图

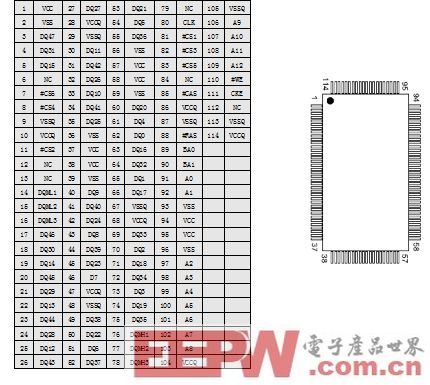

VDSD3G48引脚的功能如表1所示:

表1 VDSD3G48引脚功能说明

1.2 芯片的主要特性

1、3.3V+0.3V电源电压;

2、时钟频率高达133MHz;

3、完全同步:所有信号在时钟的上升沿锁存;

4、内部流水线操作;

5、可编程爆发长度:1,2,4,8或页;

6、自动预充电;

7、自动刷新;

8、64ms,8192-刷新周期;

9、兼容LVTTL;

1.3 芯片的操作

芯片VDSD3G48操作比较复杂,在能够进行最简单的读写操作之前必须要进行初始化和模式设置,是芯片工作在一个确定的工作模式。这些操作,包括读写操作,都是通过控制器传送命令来完成的。VDSD3G48AM有多个命令,这些命令定义如图3 VDSD3G48真值表所示:

存储器相关文章:存储器原理

评论