台积电2nm制程工艺取得新进展 2nm竞争赛道进入预热模式

据国外媒体报道,推进3nm制程工艺今年下半年量产的台积电,在更先进的2nm制程工艺的研发方面已取得重大进展,预计在明年年中就将开始风险试产 —— 也就意味着台积电2nm制程工艺距量产又更近了一步。

本文引用地址:https://www.eepw.com.cn/article/202206/435149.htm业界估计,台积电2nm试产时间点最快在2024年,并于2025年量产,之后再进入1nm以及后续更新世代的“埃米”制程。

台积电去年底正式提出中科扩建厂计划,设厂面积近95公顷,总投资金额达8000亿至10000亿元新台币,初期可创造4500个工作机会。以投资规模及近百公顷设厂土地面积研判,除了规划2nm厂,后续的1nm厂也可能落脚此处。

据台湾《经济日报》报道,台积电2nm建厂计划相关环保评审文件已提交送审,力争明年上半年通过环评,随即交地建厂,第一期厂预计2024年底前投产。

由于高性能计算(HPC)相当仰赖先进制程,而台积电在先进制程所掌握着绝对优势,是台积电之所以能够在半导体产业屹立不摇、独当一面的重要原因之一。但是先跑并不意味着先赢,关键还是在客户最终决定采用谁的制程来生产产品。

目前台积电在5nm制程的地位已经相当稳固,而有能力部署2nm先进制程的半导体公司,不外乎就是台积电、三星与英特尔三家公司。依照过去的发展,台积电最终会在良率及效能上技压群雄,进入2nm后的时代,历史是否会完美复刻?

2nm竞争赛道进入预热模式

三星作为台积电最强有力的对手,近几年的发展速度飞快,并且多次公开表示要在芯片加工领域与台积电展开竞争,计划在2030年超越台积电,成为全球最大的系统级芯片制造商。按照三星和台积电的差距来看,三星实现反超还有很长的路要走,原因在于:

· 台积电在晶圆代工领域积累了丰富的客户资源,包括苹果、华为、高通、英伟达等。对于追求先进制程迭代速率较快的企业而言,先进工艺技术的抢先且稳定,产品更早发售的市场优势非常关键。

· 产能方面,现在台积电的晶圆代工产能领先三星于三倍之多,在产能使用和保障上,台积电目前更有优势。

· 不能忽视的是台积电属于纯晶圆代工厂,而三星是一个IDM企业,自身生产的产品和一些纯IC设计厂商的产品具有竞争关系,客户也会在挑选代工厂商上有所考虑。

· 另外,以往的经验来看,三星在晶体管参数、芯片功耗、发热问题、良品率上都比台积电略逊一筹。特别是采用三星制程的芯片始终摆脱不了严重过热问题,性能也低于台积电所代工的芯片,使得三星很难扩大市场占有率。

半导体已成为战略物资,让外界更加关心全球先进制程竞赛的战局变化。在7nm和5nm制程工艺的量产时间上基本能跟上台积电节奏的三星电子,在更先进的3nm制程工艺上有望先于台积电量产,有报道称他们正推进在二季度量产。

三星电子方面已经宣布,他们早期3nm级栅极全能(3GAE)工艺将在二季度量产。三星电子宣布的这一消息,也就意味着业界首个3nm制程工艺即将量产,将是首个采用全环绕栅极晶体管(GAA)的制程工艺。

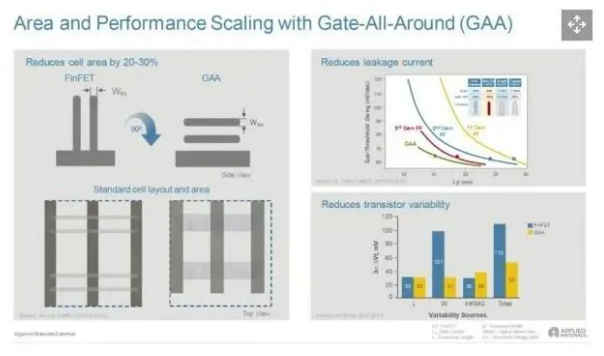

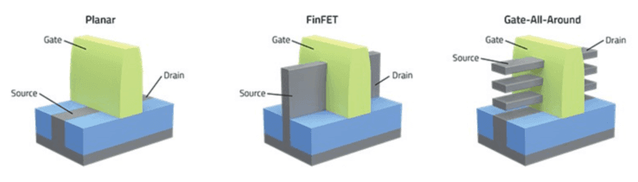

从理论上讲,与目前使用的鳍式场效应晶体管(FinFET)相比,GAAFET有许多优势。在GAA晶体管中,通道是水平的,被栅极所包围;GAA通道是利用外延和选择性材料去除形成的,这使得设计者可以通过调整晶体管通道的宽度来精确地调整它们。通过更宽的通道获得高性能,通过更窄的通道获得低功率。这样的精度大大降低了晶体管的漏电电流以及晶体管的性能变化,这意味着更快的投产时间、上市时间和提高产量。

无论三星、台积电谁将跑赢3nm之争,先进制程的王者之战,势必会延伸至2nm技术。外界有所担心的是,三星的3nm制程就采用GAA技术,2nm技术则依此延伸;但是,台积电的3nm依旧使用原有的FinFET架构,直到2nm才采用GAAFET工艺,是否会因此处于下风。

目前来看台积电已经试产了3nm芯片,预计今年将会量产。但是从研发到生产上,台积电从3nm制程到2nm制程,即从FinFET转到GAAFET还需要有一定的适应调节能力时间。

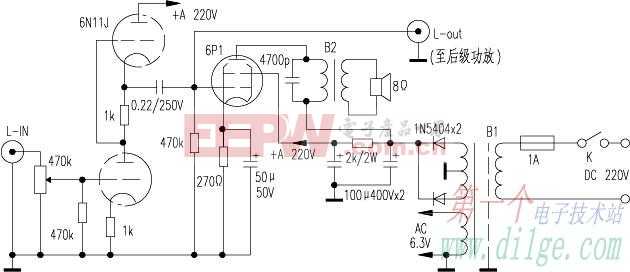

平面晶体管、FinFET以及GAA FET示意图

3nm将是一个长节点,在该节点上将有大量需求,那些对计算能效有更高要求的客户可以率先转向2nm,预计3nm和2nm将重叠并存相当长的一段时间。

作为唯一能跟上台积电脚步的芯片制造巨头,三星又有新动作。这段时间三星副会长李在镕正在欧洲进行访问,期间可能将到访ASML交涉采购EUV光刻机的事项。

除此之外,在此之前就有不少关于三星收购恩智浦的传闻,现在随着李在镕在欧洲的到访工作展开,又传出要收购的消息。不过三星收购恩智浦的消息还处在传闻阶段,并没有展开实质性动作。而且就算三星决意要收购恩智浦也没有那么容易,还需要获得各国监管的批准。

在先进制程之战中,还有两位选手值得关注,那就是英特尔和IBM。

· 英特尔公布了最新的技术路线,首先把重要工艺命名进行了修改10nm技术改名Intel 7、7nm技术改为Intel 4、5nm技术改成Intel 3、2nm技术改成Intel 20A。Intel 20A工艺也是开始由FinFET工艺转向了GAA晶体管,其中将会采用RibbonFET和PowerVia技术。

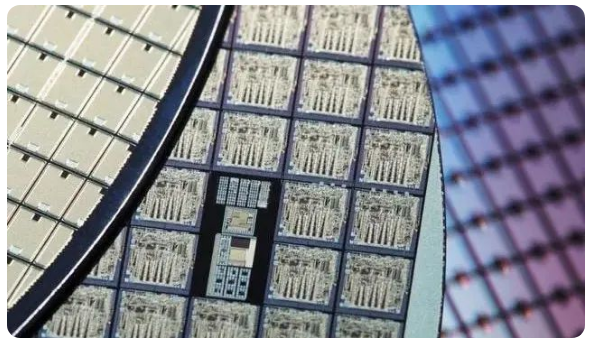

· IBM在2021年5月发布的全球首个2nm制造工艺,并在纽约州奥尔巴尼的工厂展示了2nm工艺生产的完整300mm晶圆。据预计,IBM 2nm工艺或能在每平方毫米芯片上集成3.33亿个晶体管。相比之下,台积电5nm工艺每平方毫米约为1.71亿个晶体管,三星5nm工艺每平方毫米约为1.27亿个晶体管。但是此款2nm芯片,并未实现真正产业化,这种实验室工艺与量产工艺差距很大。

2nm制程所面对的挑战

想要研发出2nm芯片,所需要的环节非常繁多且缺一不可,其中晶体管架构方式的转变和优化就是技术的象征,新型材料的选择与应用一样会起到至关重要的作用。半导体制程已逐渐逼近物理极限,因此晶体管架构的改变、新兴材料的应用、亦或是封装技术的演进都会是芯片持续提高效能、降低功耗的关键。

目前,2nm制程技术关注的重点在于晶体管架构将由FinFET正式进入GAAFET世代。相较于FinFET,GAAFET架构为四面环绕式包覆,更能有效提高效能同时控制漏电 (降低功耗)。GAAFET工艺采用的是纳米线沟道设计,沟道整个外轮廓都被栅极完美包裹,对沟道的控制能力会更好,并且拥有更好的静电特性,尺寸能够进一步微缩。

还需要考虑的是,现有的光刻机是否已经满足2nm的开发需求?当前的光刻机支持2nm工艺的研发是完全没有问题,5nm量产工艺的光刻机使用多层曝光工艺就可以实现。但是考虑到成本,2nm量产需要的光刻机目前ASML还在开发中。

据公开信息,荷兰ASML公司正在研发High NA(高数值孔径)EUV光刻机,可满足2nm的研发和生产需求。首台High NA EUV光刻机将于2023年开放早期测试,并从2025年开始量产。但具体来看,满足2nm制程生产需求的光刻机还需要突破光学分辨率的问题。同时,为适应2nm的开发需求,光刻胶也需要进行进一步的革新以满足光刻机更高分辨率的需求。

先进工艺肯定会遭遇物理瓶颈,摩尔定律也肯定面临失效风险,后摩尔时代的重点将不会聚焦在无限制提升工艺制程上面,而是通过先进封装、Chiplet、优化芯片架构,甚至提升软件层面的算法,来提升芯片的运算效率,在这些领域,可供提升的空间还很大。

后摩尔时代中,先进工艺的发展历程是否还会稳步发展下去?众所周知,先进工艺代工价格非常昂贵,民用芯片一是考虑性能,二就是价格。一个不可否认的事实是,现有的成熟工艺几乎已经完全可以满足民用类芯片的所有需求。除非在新的通信技术加持下推出需要超大算力、存储容量的爆款应用产品,否则很难让普通消费者为手机支付较大开支,来进一步大幅提升性能。

美国乔治敦大学沃尔什外交学院安全与新兴技术中心(CSET)发布的信息显示,台积电一片采用3nm制程的12英寸晶圆,代工制造费用约为3万美元,大约是5nm的1.75倍。在裸片(die)面积不变(即升级架构,不增加晶体管数量)、良率不变的情况下,未来苹果A17处理器如果采用3nm制程,成本将上涨到154美元/颗,成为iPhone第一成本部件,而5nm的A15处理器只是iPhone的第三大成本零部件。

评论