复杂系统级芯片的软件/硬件协同验证

本文针对复杂系统级芯片的软件/硬件协同验证环境的多种方法进行了分析和比较, 并就各种方法在蓝牙系统级芯片设计中的应用为例对其进行了详细地阐述。

本文引用地址:https://www.eepw.com.cn/article/193866.htm随着半导体技术的飞速发展,单个硅片上的集成度越来越高,如何更快、更有效的完成基于SoC设 计逐渐成为人们关注的焦点。目前,许多设计小组仍然沿用十万门设计中用过的工具和方法来验证庞大的硬件和其嵌入软件,这些方法往往要占用50%以上的设计 周期, 而且已经达到极限。验证最后设计的正确性被视为设计更大规模的系统级芯片的重要瓶颈。本文针对复杂系统级芯片的软件/硬件协同验证环境的多种方法进行了分 析和比较, 并就各种方法在蓝牙系统级芯片设计中的应用为例对其进行了详细地阐述。

随着近来日益明显的灵活性需求,系统级芯片设计采用软件来实现设计中的一部分硬件功能, 而不再采用单一用途的硬连接。现今,在一个复杂的系统级芯片应用中,例如视频解码器,设计者将集成硬件模块,应用软件,RTOS,片上总线,可编程嵌入处 理器I/O外围设备,内存模块,即所谓嵌入式内核系统级芯片框架。

协同验证环境

嵌入技术为基础的SoC系统的设计周期,通常首先产生一个系统设计的抽象模型并对其进行模拟, 功能抽象被映射到一个详细的系统结构,同时定义了系统框架的性能模型。系统结构映射把复杂系统分解成多个层次独立的硬件核子模块和软件核子模块核。同时系 统需求被转换为软件和硬件规范。硬件设计团队利用Verilog和VHDL完成硬件部分, 然后用硬件模拟器做验证。软件设计团队利用汇编,C,C++语言完成SoC所需的RTOS内核软件或其他功能软件如通信协议软件的设计,利用处理器模型和 ICE来测试软件。传统上,软件团队等到硬件原型完成才可进行最终的系统集成。很多问题会产生在系统集成的过程中。这些问题产生源于对规范的误解,不适宜 的接口定义,和稍后的设计变化。通过软件递归设计可以消除这些错误,但这样可能会影响系统的性能。如果利用修改硬件的方法会十分耗费金钱和时间,特别是当 其中包含循环设计集成电路。把系统的集成阶段移到设计周期的前期可以较早的消除系统集成的问题。这可以通过创建一个软件/硬件协同验证环境来解决这个问 题。

在一个软件/硬件协同验证环境中有些方面十分重要:准确,环境中模型应该时钟周期准确或者管脚准确而且必须准确地映射 SoC功能。快速,环境的速度应该足够快得可以使由实时操作系统和应用程序组成的软件运行。适用,软件和硬件设计团队都应该能够运用这个环境来进行功能和 性能验证。可得,为了实现Time_to_Market(TTM)的目标, 并能够完成硬件/软件协同设计和协同验证,环境应在设计周期的早期得到。经济,较少的金钱耗费也是一个和准确性,性能同样重要的考虑。

一般的协同验证环境会有一个源代码调试器作为基本构成,为了让用户可以下载固件/软件并连接系统。调试器可以帮助阅读源代 码,设立断点,暂停和控制处理器的运行。依靠所选择的环境的不同,处理器模块就可以被一个模拟模型所代替,诸如指令集模拟器(ISS),总线功能模型,或 者RTL代码。系统剩余的外围设备可以用C代码模型,正式芯片,RTL 码,或在FPGA中的实现来代替。

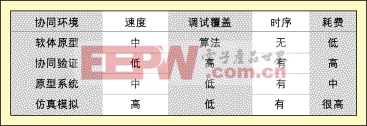

表1列举了几种协同验证环境, 它们支持在设计周期中较早地集成软硬件,可以克服由传统验证方法所带来的缺陷,同时,基于以下协同验证环境所开发的软件可以直接移植到最终的硅片上。当选取一种验证环境时,验证目标,调试覆盖,性能要求,可以利用的资源是必须考虑的要点。

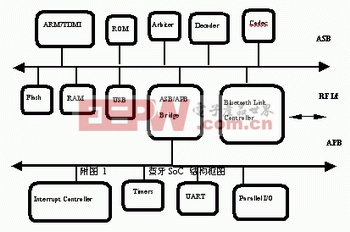

本文以后的部分将针对其中的软体原型和原型系统进行详细地阐述,并以各种方法在一款蓝牙系统芯片的设计中应用为例。附图 3 表示了举例的蓝牙系统芯片设计框图, 该设计基于ARM7TDMI处理器核和AMBA片上总线。处理器运行在RTOS上完成所有任务的管理和调度,同时运行完整的蓝牙协议栈。

软体原型

一个软件原型是被验证的设计的软件表现。 它可以检查处理器的寄存器状态,内存存取,和外围设备。如果运行软件原型主机的运行速度足够快,它可以使实际应用软件和固件在其上运行。利用软件原型可以 使设计者在得到实际硅片之前使设计者平衡所修改的系统参数和检查所得结果,测试中断处理函数,开发和测试驱动程序,测试编译器产生的代码的正确性,使系统 和外围设备的行为可视化和检验应用程序算法的正确性。

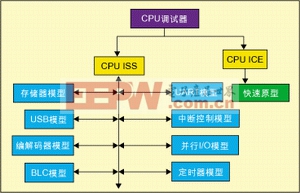

在软件原型中,处理器用一个ISS模拟,并和源代码调试器接口。外围设备用C模型表现。图1为所举例的蓝牙系统级芯片一个 典型软件原型的简单框图。它由一个CPU调试器(例如,ARM调试器)一个CPU ISS(例如ARM模拟器)和外围设备C 模型。利用软件原型开发的软件和固件可以通过ICE下载到快速原型或目标硬件系统并为仿真作配置。

建立一个基于微处理器的系统的软件原型,需要以下软件构件: 1. 处理器源代码调试器,这个软件模块由调试核和用户界面所集成,可以使使用者去控制目标系统在调试周期中所处的状态。调试、编译和(目标代码)连接工具集位 于和调试核集成的调试宿主机器。调试器可以通过一个ICE连接到目标硬件系统。调试器可以被用作读/写寄存器和内存,控制和重启系统和模拟器中的处理器。 2. 指令集模拟器(ISS),该软件模块在没有考虑时延地前提下模拟处理器指令。特定的处理器生产商会提供相应的ISS。例如,ARM 提供的ARMulator模拟ARM处理器系列,提供和外围设备C模型的接口,并帮助构成一个软件原型。3. 外围设备C模型,其中寄存器的所有细节,字节定义,外围的中断行为都应该包含在该C 模型中。这可以使固件和应用软件仅做少量的改动或不改动就可在实际硅片中使用。

在实际应用中,软件原型有以下的局限性:a. 容量有限:软件原型仅在早期接口和代码段调试应用。B. 速度有限:在大多数情况,模拟速度是一个十分敏感的问题,因为模拟器总不能和实际的处理器一种快。C. 模型的准确性:外围设备C模型仅是功能正确, 而不是时钟周期正确和管脚正确。D. 同步性:对于像外围设备数据同步性的需求一般难于解决。

构成一个软件原型必须遵行以下步骤:1. 分析为设计所选取的处理器的特征。2. 检查所选处理器ISS是否能够和所选外围C模型接口。如果ISS无相应的接口,软件原型就无法构成。3. 分析接口,内存地址,寄存器,字节定义,外围设备中断行为,并完成相应C模型。4. 完成需要利用软件原型去验证的应用程序。并将处理器ISS,外围C模型,应用程序编译成可在宿主机运行的可执行程序。5. 运行编译程序和调试器并开始调试。如果有一些错误,其起因可能是因为外围设备模型和应用程序的错误。如需要进行性能测试,则可在相应的仿真或快速原型环境 下进行,最终当实际硅片完成,软件既可被用于最后软件和硬件集成。在举例的蓝牙系统级芯片(如图2所示)的软件原型中,分别为UART,并行接口,中断控 制器模块构造C模型,ARM7TDMI处理器被ARMulator所代替。 其中ARMulator由一个ARM 处理器内核模型,内存接口, 执行环境中操作系统接口,和一个协处理器接口组成,同时和ARM调试器接口。

快速原型系统

快速原型系统(RPS)是设计的硬件设计的表现。成功快速原型的关键在于尽可能快的实现一个原型。这里将着重论述针对应用的 可重置系统原型系统(ARPS)。这种方法将目标设计映射到普遍可得的商用器件上而且具有一定的扩展能力和可重用特性。通常,这些原型的构成围绕嵌入式处 理器的BSP,通过增加附加构件(内存,FPGA,IP核)。根据所选的IP,BSP可以在SoC完成前被用来开发和调试硬件和软件。例如,很多IP供应 商,ARM,DSPGroup,MIPS,Motorola都提供基于他们处理器IP的BSP。这些BSP可划分为两种,一种基于微处理器,例如将在举例 中的提到的ARM基于AMBA的BSP。这款组成包括一个ARM7TDMI处理器芯片,仲裁器,地址解码器,内存,两个时钟,中断控制器,两个UART, 并口,两个PC卡插槽,和(闪存/EPROM,SRAM,DARM)内存控制器。BSP有辅助软件和一个ICE帮助开发和调试,它在20 MHz 时钟下,并连接LA。另一种基于DSP。较典型例如DSP Group基于OkaDSP的BSP。它的构成包括一个DSP,地址解码器,扩充内存,和胶合逻辑。它运行在40MHZ 时钟速度,可以连接LA,通过一个PC附加模块提供体调试特征。

ARPS除了具有应用范围大,性能高,支持模拟/混合信号器件(AMS)的集成等RPS的共性外。同时,ARPS具有如下 的特殊优点:首先,有助于快速理解IP功能,包括处理器和外围设备。其次可以证明设计产品的特征。有能力连接ICE和LA设备做调试。能够便利地探测和监 控系统内的管脚和信号。最后可以通过插入附加IP模块来进行设计扩展。

在实际应用中,ARPS有以下的局限性:首先将整个设计划分到多个FPGA将是一个工程挑战并占据大量的时间,这往往是因 为FPGA的最多管脚数(I/O接口)一般有限(通常400~450)。其次,除非未来的产品基于相同的平台,否则ARPS的重用仅限于选定的应用领域。 最后,也是较重要的一点,如果需要额外的功能模块,相应花费的开发时间将颇为可观。其中将包括FPGA实现,PCB封装等。

基于以上的特点,通常运用ARPS方法时总假定系统设计已经完成,软件和硬件划分已经完成,所需的SoC的IP集合和 BSP以被确定和选取。构成一个ARPS验证必须遵行以下步骤:1. 选择并分析可用IP的BSP,并将其映射到目标SoC设计。2. 如缺乏所需的IP模块,选取适当FPGA器件并完成相应RTL代码综合,模拟,和布线。3. 对相应BSP进行配置并和额外设计的模块连接。4. 利用ICE和LA调试器件驱动和应用程序代码,并分别修复软/硬件错误。

举例的蓝牙SoC的ARPS由ARM的基于AMBA的BSP构成。该BSP由架构(图3)中除了USB, 编解码器, 蓝牙连接控制模块以外的所有模块组成。遗漏的这三个模块可以集成到一个ASB模块中,并插入BSP所提供的接口。蓝牙连接控制器和编解码器的数字部分可以 在一个FPGA中实现。AMS模块(数模, 模数转换, USB模拟部分器件)可以通过标准芯片连接到外部的FPGA。有关设计可参照www.arm.com 的设计准则来完成。随BSP提供的软件工具包含一个源代码调试器、编译器=汇编、(目标代码)连接器,这些可以被用作软件的开发和调试。应用软件和固件可 以利用这个该ARPS来测试。

SoC中的调试技巧

因为没有外接管脚可以连接ICE 和LA,SoC中的处理器内核对于调试和分析是不可见的。这就需要新的调试技巧和工具去解决嵌入式内核的调试和分析问题:BDM核,基于扫描链的调试方法(JTEG)和Nexus 5001 Forum:

1. BDM 已经被融入Motorola 微处理器。这是通过增加一个小的调试逻辑和附加的微处理器代码来实现。这种模型使用一个外在处理器来控制微处理器的目标系统并通过串口检测内部寄存器和内 存,而目标系统和主系统的联系通过一个BDM导线。BDM技术不需求任何目标处理器资源,例如片上内存和I/O管脚。

2. JTAG (IEEE 1149.1) 标准源于边界扫描,一开始为芯片制造的测试所设计。该标准同时可以执行器件内测试,例如ATPG和BIST。

很多内核供应商和半导体公司利用JTAG 标准来实现仿真模拟,通过添加调试逻辑去测试处理器内部寄存器,指令,数据线内容,还可以通过设立断点控制软件的执行。处理器内核,例如ARM, MPIS和POWERPC 都有基于JTAG的仿真模拟特性。

3. Nexus 5001 Forum 建立于1998, 定义了一个嵌入式处理器调试和接口标准。该标准为处理器和构架独立而且支持多内核和多处理器的设计。 Forum 由处理器供应商,工具供应商,和器件制造商组成, 同时也称为IEEE-ISTO 5001 标准, 有关可参照www.ieee-isto.org/Nexus5001。

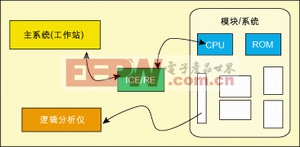

任何调试技巧都依赖于一定的工具。调试工具分两种,硬件工具和软件工具。硬件调试工具用于调试硬件目标系统。 它包括ROM模拟器(RE)、ICE和LA. 图2显示 ICE /RE,LA和硬件模块之间的连接,其中ICE连接CPU,RE连接系统ROM。

一个RE插入目标硬件原型上ROM/FLASH插口,映射目标ROM到内部ROM,这可以快捷地完成代码修改,通过消除EPROM擦/写周期加速调试过程。ICE是一个硬件设备,物理代替并模拟被测目标系统的处理器。而LA则被用作目标系统的高速数据采集。

软件调试工具则包括ISS 和cycle accurate simulator(CAS)。模拟器是一种软件工具以用来仿真处理器的功能。它和外围设备的C模型接口,在得到实际硅片前建立一个代表目标设计的系统。 这可以使开发者开始开发固件,驱动程序和应用程序。对于前者,顺序执行程序指令并不考虑系统时钟。而对于CAS, 处理器的行为以时钟周期为基准,处理器内部细节,例如流水线,处理器接口,总线协议,都可以做详细地模拟仿真。通常情况下,ISS的速度较CAS快。

本文小结

在复杂SoC器件中协同验证硬件和软件需要新的方法和工具。随着软件数量在即所谓基于嵌入式内核系统级芯片框架的系统级芯片 上的不断增加,设计周期中较早地集成软硬件是至关重要的。本文重点阐述了软件/硬件协同验证的基本特征,四种较为完善的协同验证环境及其各自特点。并以蓝 牙系统级芯片设计中的应用为例针对其中的软体原型和原型系统进行详细地阐述。提供一个完整的基于软核和硬连线宏功能块的硬/软件验证和调试的解决方案。

c++相关文章:c++教程

加速度计相关文章:加速度计原理

评论