基于FPGA的级联结构FFT处理器的优化设计

0 引 言

数字信号处理主要研究采用数字序列或符号序列表示信号,并用数字计算方法对这些序列进行处理,以便把信号变换成符合某种需要的形式。在现代数字信号处理中,最常用的变换方法就是离散傅里叶变换(DFT),然而,它的计算量较大。运算时间长,在某种程度上限制了它的使用范围。快速傅里叶变换(FFT)的提出使DFT的实现变得接近实时,DFT的应用领域也得以迅速拓展。它在图像处理、语音分析、雷达、声纳、地震、通信系统、遥感遥测、地质勘探、航空航天、生物医学等众多领域都获得极其广泛的应用。随着FPGA技术的高速发展以及EDA技术的成熟,采用FPGA芯片实现FFT已经显示出巨大的潜力。

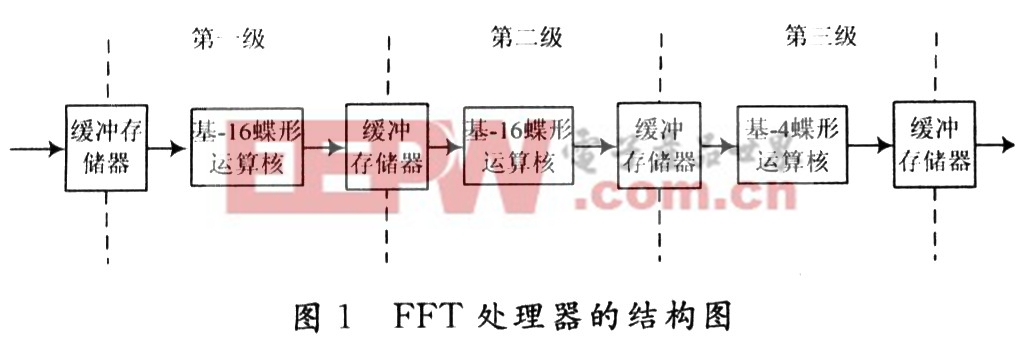

目前用FPGA实现的FFT处理器结构大致分为四种:递归结构、级联结构、并行结构和阵列结构。递归结构只利用一个碟形运算单元对数据进行规律的循环计算,使用硬件资源较少,但运算时间较长。级联结构每一级均采用一个独立的碟形运算单元来处理,相对递归结构速度上有所提高,不足之处是增加了延时用的缓冲存储器使用量。并行结构对一级中的蝶形单元并行实现,阵列结构是将每一级的蝶形运算单元全部并行实现,这两种结构有很高的运算速度,但消耗的资源过大,一般不采用。为了提高运算速度,特别是为了适应多批数据处理,一般采用级联结构实现FFT处理器。

1 FFT整体结构设计

在FFT算法中,目前大多使用基-2和基-4算法实现级联结构的FFT处理器,除此之外,也可采用基-8和基-16算法来实现。随着基数的增大,对于相同点数的离散数列,处理器所分的级数越少,对缓冲存储器的需求也越小,因此考虑采用基-16算法来实现FFT处理器,但基-16算法只能实现离散数列点数是16的p次幂的FFT。从而,引入混合基思想来改进基-16算法。

设x(n)为N点有限长序列,其DFT为:

式中:n1=0,1,2,…,r1-1;n2=0,1,2,…,r2-1。将频率变量k(kN)表示为:

k=k1r1+k0

式中:k1=0,1,…r2-1;k0=0,1,…r1-1。

式(1)可变换为:

设r1=16P,r2=N/16P=2,4,8,式(2)先将原非16的p次幂的N点FFT分解为16P点的FFT;再分解为N/16P点的FFT。首先对输入信号进行16P点的FFT运算,然后将结果乘以一个旋转因子最后将计算出的数据进行一次N/16P点FFT运算,得到的结果即为所需要的N点FFT运算结果。这样处理,既能减少分解的级数,又能使计算离散数列点数只需是2的整数次幂即可。以1 024点为例,只需分解成两级基-16运算模块和一级基-4运算模块即可实现,其FFT处理器结构图如图1所示。在此结构图的前端增加/减少基-16运算模块或将最后一级基-4运算模块改为基-2或基-8运算模块,就可以实现其他离散数列的点数只需是2的整数次幂的FFT运算。

评论