全芯片混合讯号设计解决方案

在数字IC设计的早期时代(1960年代初期),电路都是手工制作,电路图(图解)都是用纸、笔和油印方式手绘而成。这些电路图说明逻辑闸与相关运作功能,用以建置设计及其中的联机。

本文引用地址:https://www.eepw.com.cn/article/190997.htm每个设计团队至少会有1位成员专精于执行逻辑、最小化与最佳化,最终导致更换1整群的通讯闸,以更快的速度执行同样工作或者占用更少的硅芯片面积。

执行功能验证–检查设计是否按照计划运作,通常由1群工程师来执行,围坐在桌边一边看着电路图,一边说道:「呃,我觉得没问题!」。同样地,时机验证–检查设计是否符合所需的输入/输出与内部路径延迟,而且没有违反与任何内部缓存器(例如setup与hold参数)都是运用铅笔和纸张来执行。

最后,用来排列逻辑通讯闸的结构以及彼此互连的整套图,全都是手绘的。这些由正方形和长方形…等简单图形构成,会被用来制作光罩(photo-mask),然后使用光罩制作实际硅芯片。

按照当今术语分类为「完全自订」的最早的数字IC,因为构成个别组件的每个几何元素的尺寸与外形都是分别手绘的。为了解决耗时及容易出错缺点,电路图绘制(schematic capture) 软件包于是出现。在抽象的通讯闸层建立数字设计,就好像使用汇编语言制作软件程序一般。

就效能与内存容量而言,组合程序堪称为优良的建置,但是制作(capture)与验证非常耗时,而且不易移到其它计算机延续开发。同样地,通讯闸层描绘的制作与验证也颇费时,且不容易移到新的晶圆厂或制程。

解决方案一旦必须转移到C等程序规划语言进行更高阶的开发时,高阶描绘就会转译成计算机所要求的机器语言指令。其优点是让软件开发人员迅速掌握程序意图,进而验证功能。此外,以C语言撰写的程序也很容易移到其它计算机平台。

一旦数字逻辑设计员开始转移到所谓RTL(Register Transfer Level)的更高阶的抽象化,就可以使用1980年代后期与1990年代初期登场的逻辑合成(Logic synthesis)技术,将RTL描绘转译成为对应的通讯闸层电路表(netlist)。这种「前端」合成技术获得「后端」自动化布局与绕线(place-and-route)引擎补强,此引擎能取得通讯闸层电路表,并执行设计实体建置。

小型设计上,合成引擎在通讯闸层抽象化的成果,可能无法媲美手绘设计。但除了迅速而且简洁地掌握设计意图,大幅提高设计人员生产力外,合成引擎自动执行速度与面积取舍的能力,在在表示出合成引擎整体表现还是较手绘更好。

模拟工具的演进

模拟电路的计算机辅助设计与验证工具发展,远早于数字电路。晶体管、电阻、电容与电感器…等独立组件设计工作,通常会先建立设计的实体原型,再将之纳入测试,测量实际值,以判断其效能,调整组件值并因应必要新增/移除组件,以达到成效。

60年代后期与70年代初期,许多大学与商业公司着手开发模拟仿真器。这些程序让学生与工程师们能仿真模拟电路运作,而不必实际建立电路。最著名的早期仿真器是加州大学柏克莱分校开发的Simulation Program with Integrated Circuit Emphasis(SPICE) ,在70年代初期广受欢迎。

几年下来,模拟仿真器在基本模型与算法演进下,及仿真引擎效能方面有了长足的进展,现今模拟设计与验证工具,基本上都受限于绘制与仿真晶体管层电路图。

• 以高度抽象化的方式描绘模拟功能,然后运用这些描绘来产生晶体管层等效电路。

• 自动使模拟电路最佳化。

• 自动布局与绕线模拟电路。

结果就是模拟集成电路,仍然绝大多数采自订、且需手工绘制方式进行。除了昂贵、耗时而且错误百出外,这种晶体管层设计作法无法让既有设计轻松转移到新的晶圆厂或制程/技术节点,反而设计的移植必须打从建置电路开始。这说明了最先进的数字设计已堂堂迈入45奈米技术,但最先进的模拟设计仍停留在90奈米,甚至许多模拟设计仍深陷130奈米和250奈米的泥淖中,而这是5到10年前的技术。

混合讯号工具演进

截至目前为止,真正混合讯号解决方案方面的工具进展相当缓慢。如前所述,为满足成本、尺寸、重量与耗电需求,模拟与数字功能将会结合在单一「混合讯号」装置上,有些EDA公司还尝试「栓合(bolt together)」既有的模拟与数字仿真引擎。

传统上,专精于数字设计的公司大多尝试购买既有、成熟的模拟解决方案,藉以来解决问题。动机就是要透过取得模拟公司的客户基础扩大市占,但结果还是无法整合一大堆零散片段工具。即使是当代「最新」混合讯号与完全自订设计环境,数字与模拟设计团队都还是各干各的,甚至完全不知道对方在做甚么。2个领域的人员在芯片完成时才首度看到对方的情形屡见不鲜,此时模拟与数字区块早就已布局、绕线完毕了。然而芯片的完成通常都是手工作业,包含芯片投产(tapeout)前才会发生的许多工作。因为缺乏自动化,芯片完成的作业与处置通常都无法回馈到主设计流程,导致未来设计中重复运用的重大问题。(本文由MAGMA产品经理提供)

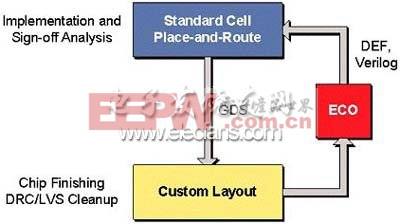

图说:在传统设计环境中,自订布局以及标准单元布局与绕线之间的循环可能会增加好几个星期的芯片开发时间。

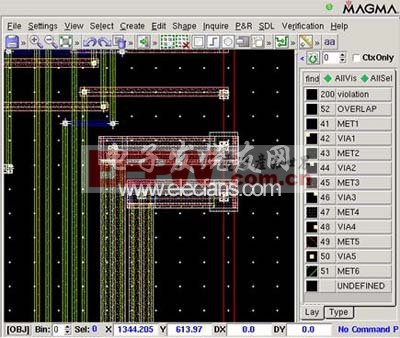

图说:Titan Chip Finishing系统包含线路布局编辑软件,并提供完整Quartz LVS验证解决方案。

图说:Titan自动布线可让生产力更为提升。

评论