基于FPGA的IRIG-B(DC)码解码

摘要:在分析了IRIG-B(DC)码码型特点的基础上,提出了一种IRIG-B(DC)时间码解码的设计方法。该方法由少量外围电路与一片现场可编程门阵列(FPGA)芯片组成,来实现对IRG-B(DC)码的解码、1 PPS信号输出、实时时间显示以及串行异步通信。与传统的方法相比,该设计方案具有体积小、成本低、工作稳定等优点,完全能够替代传统的B码机箱的功能。

关键词:IRIG-B(DC);FPGA;硬件描述语言;串行通信

随着电力自动化水平的提高,电力对时间的同步要求越来越迫切、时间同步的精度要求越来越高。采用GPS全球卫星定位系统的时间同步功能,是提高电力生产和管理自动化水平、确保运行质量的一条最佳途径。国家电力公司、各大电网和省电力公司,高度重视电力系统的时间同步系统的建设,明确要求电力的生产运行系统装置采用卫星时钟进行校时。由于目前GPS接收机采用IRIG-B(DC)时间码的格式输出标准时间信息,所以本文提出了一种基于FPGA来实现的IRIG-B(DC)时间码解码设计方案。

1 IRIG-B码简介

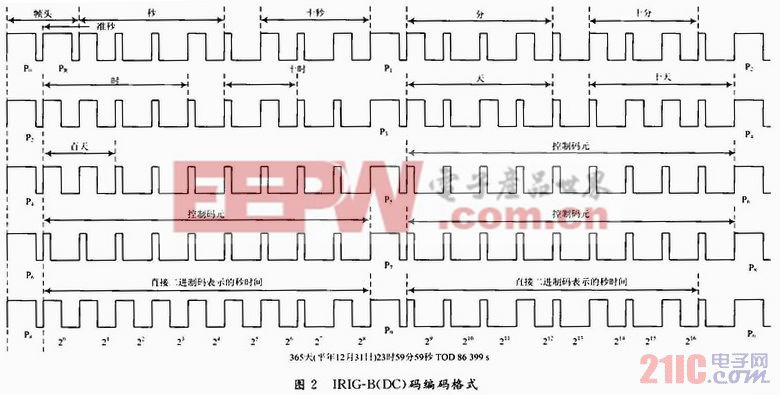

IRIG-B(DC)时间码(简称B码)是由IRIG所属的TCG(Telecommunication Group)制订的一种串行时间码。B码是一种串行时间码,帧长为1 s,共包含100个码元。它采用脉宽调制方式编码,共有三种宽度的码元,分别表示“0”,“1”.“P”,其中“P”为标志位,如图1所示,码元的总宽度为10 ms,“0”的脉宽为2 ms;“1”的脉宽为5 ms;“P”的脉宽为8 ms。

B码的1帧从连续两个“P”开始,其中第一个标志位为P0,第二个标志位为PR,PR的上升沿是1 s的准秒时刻,即当前帧表示的秒时刻的起点。如果规定PR所在位置为第0个码元,那么每帧分别有编号为0,1,2,…,99的码元。标志位P1,P2,P3,…,P0的位置分别在9,19,29,…,99。B码包含了当前时刻的秒,分,时,天信息和每天按秒计时的秒数(TIME OF DAY,TOD),如图2所示。

评论