40纳米500MHz DSP核心的时钟设计与分析

在低于40纳米的超深亚微米VLSI设计中,时钟树网络在电路时序收敛、功耗、PVT变异容差和串扰噪声规避方面所起的作用要更重要得多。高性能DSP芯片会有大量关键时序路径,会要求时钟偏斜超低的全局时钟分布。两点间时钟偏斜若不合要求,特别是如果这些点间还存在数据路径的话,可能会限制时钟频率或导致功能性错误。

本文引用地址:https://www.eepw.com.cn/article/170846.htm本文中所描述的是以500MHz时钟频率运行的DSP核心,多数时序关键路径都有超过20级的逻辑层。考虑到时钟抖动率和建立时间,满足高频需求真的是项非常具有挑战性的任务。如果使用传统时钟树设计方法,我们至多能获得全局时钟偏斜为150ps的时钟树。而在早期STA阶段,我们会发现由于时钟偏斜不平衡而导致的从-100ps到0ps的建立时序违规高达1万多条。这些均使得偏斜较低的时钟设计方法成为了一种迫切需要,而且还要求这种方法应能够改善时钟PVT变异容差并降低功耗。

用以衡量DSP时钟树分布结果质量(QOR)的参数主要有三个:一是RC分布扩展;二是插入延时扩展;三是同级延时扩展。我们将比较新时钟设计方法与传统方法,产生时钟衡量指标。

时钟设计

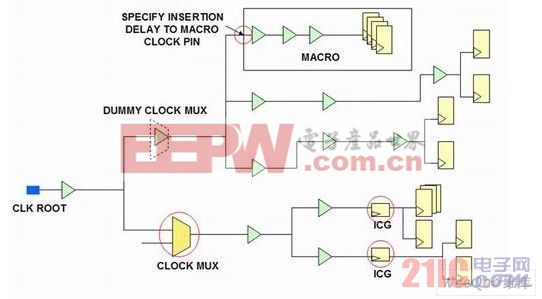

本文中40nm 500MHz DSP设计使用了一种可覆盖整个功能块的单节点、双相全局时钟,在这个案例下我们将其称为CLK。DSP的时钟结构如图1所示,CLK可驱动超过 5.3万的触发器,因此我们建议采用一种有效的设计方法来创建更鲁棒的低偏斜时钟。

图1 DSP功能块的时钟结构

时钟缓冲器选择

驱动强度超低和超高的时钟缓冲器都是隐藏的。

隐藏超高驱动强度单元有以下优势:降低由于打开关闭高驱动单元而导致的局部时钟树功耗和动态IR违规;缩短每级时钟的有效网路长度。

隐藏超低驱动强度单元有以下优势:减少时钟树根上缓冲器总数;避免EM问题的潜在风险性。它也将带来一些劣势,比如:可能潜在地提高时钟插入延时;可能导致同样插入延时具有更高时钟树功耗(同时减轻局部动态IR降热点)。

在此我们还禁用了时钟树反相器(CTI),因为它将导致毫无差别的时钟树拓扑结构。而且我们还发现微捷码工具用来创建只有缓冲器(buffer-ONly)的时钟树拓扑结构会比用来创建混合型时钟树拓扑结构更有效。

时钟斜率控制

非可控性斜率违规不仅会导致时钟插入延时的增加和电学DRC违规,而且还会造成不符合通道热载流子规则的设计违规。在本文中,我们使用了以下两种方法来控制好时钟斜率:

1)限制每个时钟树单元(icg、ctb) 的扇出。

2) 在CTS过程中使用微捷码Talus命令明确定义时钟树斜率范围,当依据全局‘斜率’范围所设置的斜率范围还不如这个范围严格时则以这个范围为准。

force limit slew $m/mpin:clk -clock 250p -context $m

增强区别于微捷码自带“fix clock”的选项/方法

微捷码提供了一个名称为‘fix clock’的可预先创建时钟插入脚本。微捷码自带CTS围绕两个命令为中心:i)“run route clock”(RRC) ,创建初始时钟树;ii) “run gate clock”(RGC),调整RRC所创建的时钟树。

RRC有个默认值为2.0的隐藏选项。时钟树布线器可根据这个选项的指示,通过2.0因子超速驱动时钟单元,其效果会比根据其时序弧报告指示来得更好。虽然这个选项可能用于高驱动单元时是极为理想,但当高驱动单元处于隐藏状态时它达不到最佳结果。如果我们发现时钟树处于缓冲状态时,那可能就是出于这项功能的原因。

对该设计进行的各项实验均显示出,这种开关的最佳值为1.5。在本文中,微捷码自带CTS脚本通过编辑可加入这个隐藏的开关。

到RRC的最后,默认使用标准全局和信号布线器执行时钟布线。微捷码自带CTS中标准全局和信号布线器用于65纳米以上设计可能已足够准确,但若用于40纳米设计则还需要在RGC之前执行精确的详细布局和高强度全局布线,这样才可确保到时RGC时有准确的时序信息来调整时钟偏斜。

RGC后,建议再进行一次详细布局和高强度全局布线来完成RGC中新添加的时钟偏斜缓冲器的布局,这样才能为CTS后进一步时序优化提供必要时序信息。

评论