40纳米500MHz DSP核心的时钟设计与分析

时钟串扰规避

在本文中,一直使用非默认时钟网路规则来降低串扰影响。如下所示,选择较高MET层进行时钟网路布线:

rule layer preference Mn clock /sr70

rule layer preference Mn+1 clock /sr70

我们一直建议采用具有2倍宽和3倍间距的NDR(Non-default Rule)来降低耦和度。事实证实,这对PTSI有很大帮助。微捷码工具中所定义的非默认规则。这种规则只应用于MET3及更高层,同样还只应用于时钟网络中非叶级网路。

时钟分析

时钟分析是采用已开发的脚本,产生时钟树分布指标,*估时钟树的结果质量(QOR)。

RC分布扩展

RC延时分布是可用以改善设计期间时钟树鲁棒性的第一个指标。时钟树RC延时百分比等于互连线延时在每个接收端(sink)总插入延时中所占比率。

对于每个时钟网路:

%RC delay = [RC delay ]/[RC delay + Gate delay]

窄(10%)分布意味着良好的跨角点时钟延时追踪。互连线在时钟路径占主导地位与门在时钟路径占主导地位相交叠的机率比较小。这种分析不包括数据路径时钟树。

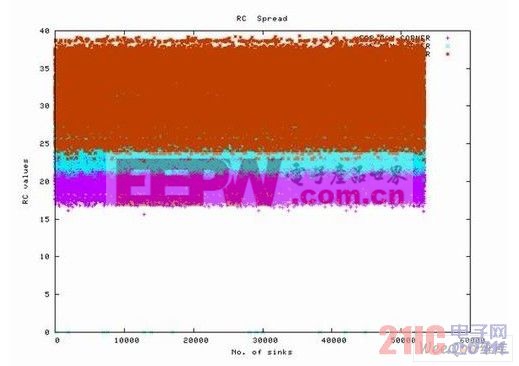

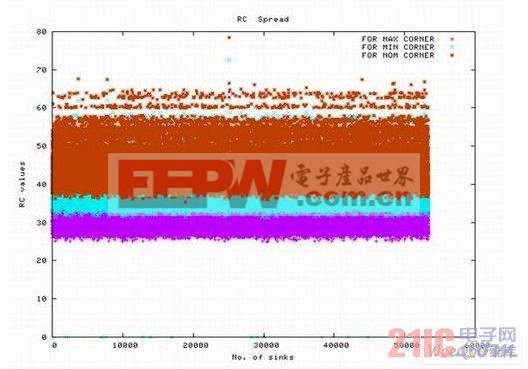

图2显示了一种更好的RC扩展分析 。在图3中,采用了微捷码自带CTS的NOM角点RC扩展率在25%以上,而图2的则在15%左右。在图3中,MAX 角点RC扩展率在10%左右,而图2的则在5%左右。

图 2 使用新时钟设计方法的RC扩展

图3 使用微捷码自带CTS的RC扩展

评论