基于NiosII软核处理器的步进电机接口设计

摘要:NiosII软核处理器是Altera公司开发,基于FPGA操作平台使用的一款高速处理器,为了适应高速运动图像采集,提出了一种基于NiosII软核处理的步进电机接口设计,使用verilog HDL语言完成该接口设计,最后通过OuartusII软件,给出了实验仿真结果。

关键词:SOPC;步进电机;硬件描述语言;软核

电子技术发展日新月异,控制技术也发生了革命性的变化,特别是SOC技术的发展,文中主要研究的是远程控制系统中步进电机控制模块设计。首先,根据控制功能的要求设计了步进电机控制模块,该模块采用一种脉冲叠加算法,实现了对步进电机任意频率变速;然后,将该模块封装到SOPC Builder的标准模块库中;最后,利用SOPC技术,在Altera公司的Cyclone II EP2C35芯片上集成了NiosII软核,相关的外围控制器和自定义的电机控制模块,完成了该设计的验证工作。

1 基本原理

步进电机是一种把电脉冲信号变换成直线位移或角位移的执行元件。步进电机的转子做成多极的,定子上嵌装有多相不同连接的控制绕组,有专用电源供电。每输入一个脉冲,步进电机就前进一步,故又叫做脉冲电动机。其角位移量与脉冲数成正比;线速度或转速与脉冲频率成正比。本文是针对的四相反应式步进电机而设计的控制器,它的定子磁极上增加了小齿,转子也做成多极的,定、转子的齿距相同,齿数也适当的配合。这样,在一对磁极下,定、转子齿在对正时,下一相绕组下的定转子齿错开t/m(t为齿间距,m为相数),再下一相绕组下定、转子齿错开2t/m,并以此类推,在定子磁场的作用下,由于转子力图取最大的磁导位置,所以每一拍,转子转过相当t/m齿矩的角度(步距角):

步进电机常用的有四相,也有三、五、六甚至更多相。相数和转子齿数越多,步矩角就越小,在同样的脉冲频率下,转速越低。

2 电机控制模块结构设计

2.1 概述

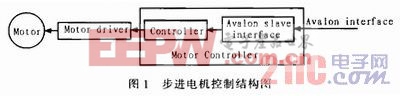

步进电机控制主要由电机控制器和电机驱动器两部分组成,如图1所示。其中,电机控制器用于控制产生脉冲,电机驱动器用于控制输出信号的功率放大。本文主要设计电机控制器。从图1可知,在电机控制器中含Avalon总线接口。在整个NiosII系统中电机控制器作为一个从设备使用。

电机控制系统的工作过程是:当控制电机的命令信号经网络发出,传给NiosII后,NiosII通过Avalon总线将信号传给电机控制器,将这个信号作为电机控制器中controller的输入,然后电机控制器会自动的输出4相控制步进电机的脉冲信号,这些信号再经过电机的驱动器的功率放大后,就可以直接驱动电机运转。可以看出其中的controller是整个电机控制模块的核心。这里的contorller模块又由3部分组成:脉冲

发生控制器、脉冲发生器、脉冲分相器。脉冲发生控制器主要是为脉冲发生器提供基准脉冲和和标记脉冲个数的寄存器值。然后通过脉冲分相器的作用来控制电机的脉冲信号CP。

2.2 脉冲发生器方案的提出

根据整个系统的设计要求,电机控制器需具有基准时钟65 536 Hz;输出脉冲的个数设定范围1~16 777 215;输出脉冲的速率设定范围1-65 535 pps。根据上面的要求,所以需要用一个16位的计数器来实现不同脉冲的信号的输出,而不同频率的输出脉冲之间不能重叠。

有了16种不同的频率而且互不重叠的基脉冲后,就可以提取16种频率的脉冲作为叠加脉冲,从而得到0~65 535范围内的连续可调的脉冲频率。

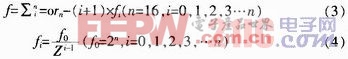

式中:f为要得到的频率;fi为各个叠加频率;f0基准脉冲;rn-(i+1)第n-(i+1)个寄存器。

文中取n=16,所以16个寄存器组成的16位二进制数的范围就是0000~FFFF。根据公式(3)、(4)可知,只要f0等于65 536 Hz,那么通过改变二进制数(r15~r0),输出f就连续可调。该电路也就是脉冲发生器(step_wave)中的核心电路。

2.3 电机控制模块设计

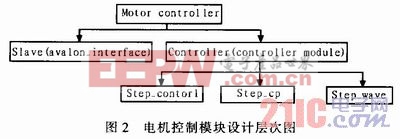

一般步进电机的控制器可以通过单片机来实现,本文电机控制模块是用verilog HDL语言实现、以IP模块的形式封装在SOPC Builder的IP模块库中,它是可以被NiosII系统直接调用的。图2为电机控制模块的设计层次图。

1)脉冲控制器

根据脉冲控制器要实现的功能,可以确定脉冲控制器主要是由以下几个小模块构成:标准频率产生模块;总输出脉冲数控制模块;输出的脉冲个数寄存器更新模块。

2)脉冲发生器

脉冲发生器的功能是产生需要的脉冲序列,经过分析后知道,此部分主要由以下几个模块构成:

①16 bit计数器,脉冲发生器最终输出的脉冲其实是由1/2CLK、1/4CLK、1/8CLK…1/32 768CLK这16种脉冲组合实现,CLK是由step _control分频得到基准时钟。为了实现这16种频率的脉冲,需要16bit的计数器。16bit计数器的产生16种状态,保持16种基频的状态唯一。

②基频产生模块,由公式(3)、(4)可知,这16种脉冲其实是以16bit计数器的16种不会重叠的状态为条件而产生的。

③脉冲叠加,脉冲叠加模块,用来把这16种脉冲叠加起来,得到需要合成的输出。最终合成的输出控制可由16个两输入与门来实现,一端接输出脉冲,另一端接对应的脉冲个数寄存器。

3)脉冲分相器

由于是四相步进电机,并以单拍的方式运行,所以在最后从脉冲分相器输出的频率为四相。CP[3:0]就是最终输出的四相信号。

3 电机控制模块的仿真与验证

1)功能仿真

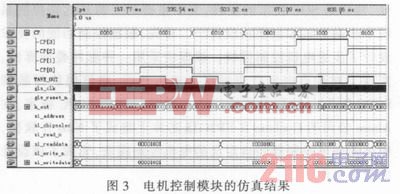

电机控制模块在Quartus II上的综合结果如图3所示,电机控制模块是由slave、step_control、step_wave及step_cp 4部分组成。

2)SOPC平台验证

首先导入的HDL文件是用于描述模块的硬件逻辑功能。对于电机控制模块,导入的文件分别是motor.v、step_control.v、step_wav e.v和step_cp.V,其中motor.V是顶层文件,配置SOPC平台,如图4所示。

当通过SW开关设定不同的值时,相应控制电机的4路脉冲信号就可以通过led显示出来。同时,利用Quartus II中的signaltap II的对电机控制模块仿真如图5所示。仿真结果是与实际设计相符的。

4 结论

根据控制功能的要求,文中设计了步进电机控制模块,该模块采用一种脉冲叠加算法,实现了对步进电机正、反转控制;实现了对步进电机转动的定位和任意频率变速。完成了对该模块向SOPC Builder的标准模块库中的封装。

结合Avalon总线、Nios II内核及其外设的特点,使用Quartus II和SOPC Builder存Cvclone II上创建了一个远程控制的硬件平台。

评论