新型雷达数字电路便携式自动测试系统设计

引言

本文引用地址:https://www.eepw.com.cn/article/109083.htm雷达,作为一种重要的军事武器装备,在军事上将其形象的比喻成作战指挥员的“眼睛”,在维护国家安全及领土完整中发挥着举足轻重的作用。但随着数字电路设计及制造技术的发展,特别是CAD设计软件的进步及完善,单一的测试方法如ICT(In-Circuit Test)测试、功能测试等已无法满足新型雷达数字电路测试及故障诊断的要求,边界扫描测试将成为今后雷达装备数字电路故障诊断发展的主流技术。

基于对ICT测试、功能测试局限性的深入探讨,以及对边界扫描测试技术的研究与实践,本文提出了“MERGE(组合)”边界扫描测试模型的建立方法,并基于此方法,构建了数字电路便携式自动测试系统,实现了对新型雷达数字电路的高速、准确的测试。系统具有硬件设备小巧、便携,性能稳定、可靠,故障隔离率高等优点,适合于战地级实时维修保障,是大型在线测试、功能测试平台的有效补充,较好的解决了测试设备受制于人及战时应急抢修等问题。

自动测试系统实现

“MERGE(组合)”测试模型的建立

IEEE 1149.1标准明确的规范了边界扫描构建原理及相应的测试方法。在故障诊断过程中,可利用VLSI芯片自带的边界扫描结构及相关测试指令,有效的实现对VLSI芯片引脚固定型、开路、桥接等故障类型的检测。但待测试的数字电路模块通常包括边界扫描器件和非边界扫描器件,本文提出的MERGE测试模型可通过已有的边界扫描结构实现对非边界扫描芯片的测试,能够拓展边界扫描的测试范围,提高TPS的故障覆盖率。

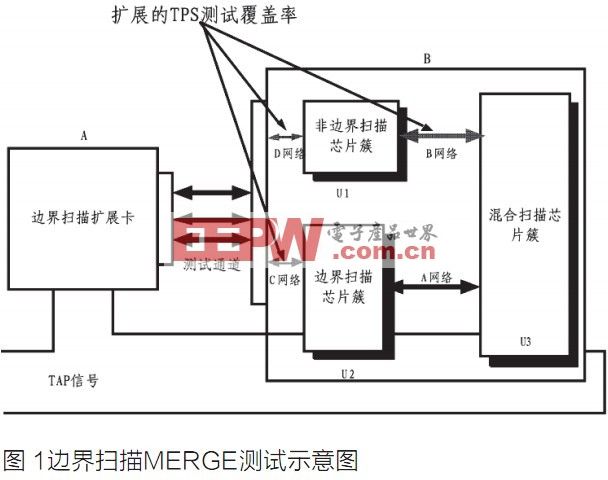

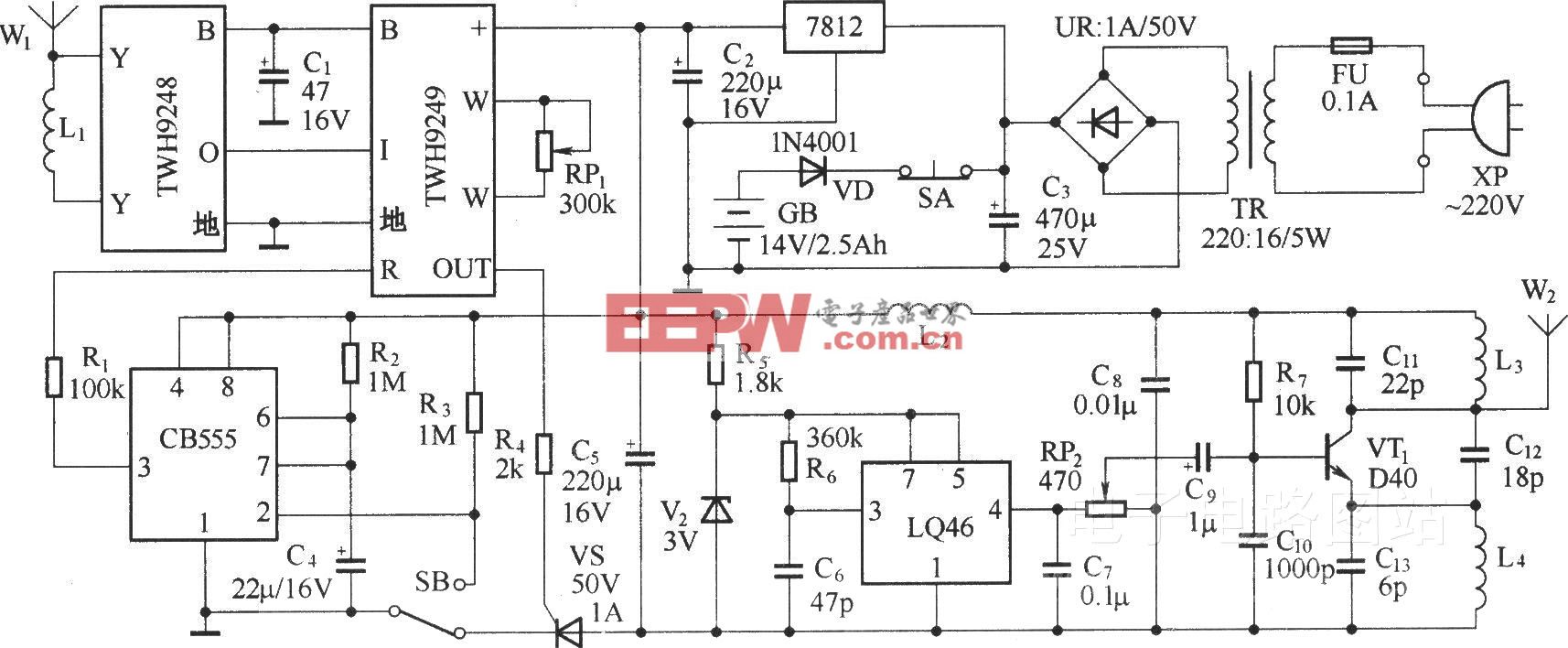

基于边界扫描测试技术的基本原理,构建测试系统过程中创造性的提出了“MERGE”结构测试模型,基本思想如图 1所示。其中,B部分为待测数字电路BUT(Board Under Test),A部分为独立于BUT外的边界扫描扩展卡,该扩展卡可看作是一块符合IEEE 1149.1边界扫描设计规范的数字电路。首先,集中将一个完整的数字电路BUT分为如下几个部分:非边界扫描芯片簇(U1),边界扫描芯片簇(U2),混合芯片簇(U3)。在这里“簇”的概念即将多个器件统称为一个“簇”,簇的范围可以根据具体电路规模来进行划分,可以小到单独的一个IC或UUT(Unit Under Test),也可大到一个完整的BUT 。

(1) MERGE非边界扫描芯片簇(U1):非边界扫描芯片是整个BUT网络中一个有序的子集,是具有特定功能的电路。在MERGE理念中,通过对非边界扫描芯片簇建立单独的功能模型,将其作为边界扫描芯片间的一个中间级信号传输模型,MERGE到边界扫描链路,结合EXTEST边界扫描指令,通过Capture IR→Shift IR→Update IR→Capture DR→shift DR→Update DR等相应操作,达到通过边界扫描链路实现对非边界扫描簇测试的目的。

评论