新型雷达数字电路便携式自动测试系统设计

(2) MERGE混合芯片簇(U3):混合芯片簇指既含有非边界扫描芯片,又含有边界扫描芯片的混合电路(还可以含有一些中间级的模拟电路)。MERGE的思路与(1)类似,模型的验证可通过将一组确定的测试矢量集APPLY至MI(Model Input),经过确定的时间延迟,通过在MO(Model Output)将采集到的响应信号与寄存器中存贮的期望值相比较的方法实现测试。

本文引用地址:http://www.eepw.com.cn/article/109083.htm(3) MERGE BSEC(边界扫描扩展卡),通过BSEC实现对BUT边缘电路中非边界扫描芯片簇或不含边界扫描芯片的BUT进行边界扫描测试。测试时,将待测BUT作为非边界扫描簇或混合边界扫描簇,而将BSEC当作边界扫描芯片簇,通过MERGE方法,将BUT、接口电路、边界扫描扩展卡电路虚拟成为一个含边界扫描芯片的BUT,具体实现与(1)、(2)类似。

测试系统硬件设计

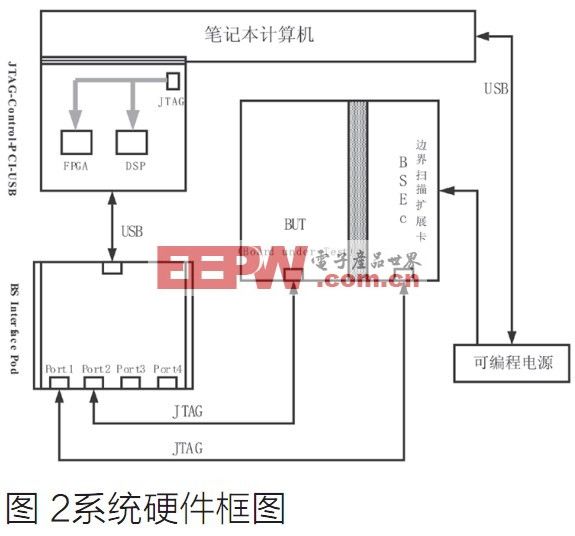

为了减轻系统整机的重量,便于运输及携带,本测试系统前端设备采用笔记本计算机作为主体来完成系统功能的实现和人机界面的交互[3],同时内配GPIB-USB模块、JTAG-Control-PCI-USB控制器,分别控制可编程电源(Agilent 6600)及BS Interface Pod模块。整个硬件设计的核心为BSEC、JTAG-Control-PCI-USB控制器及BS Interface Pod模块。其系统硬件框图如图2所示。

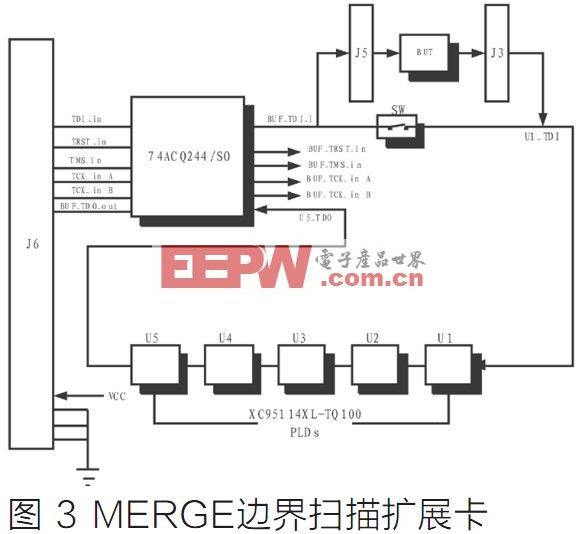

边界扫描扩展卡

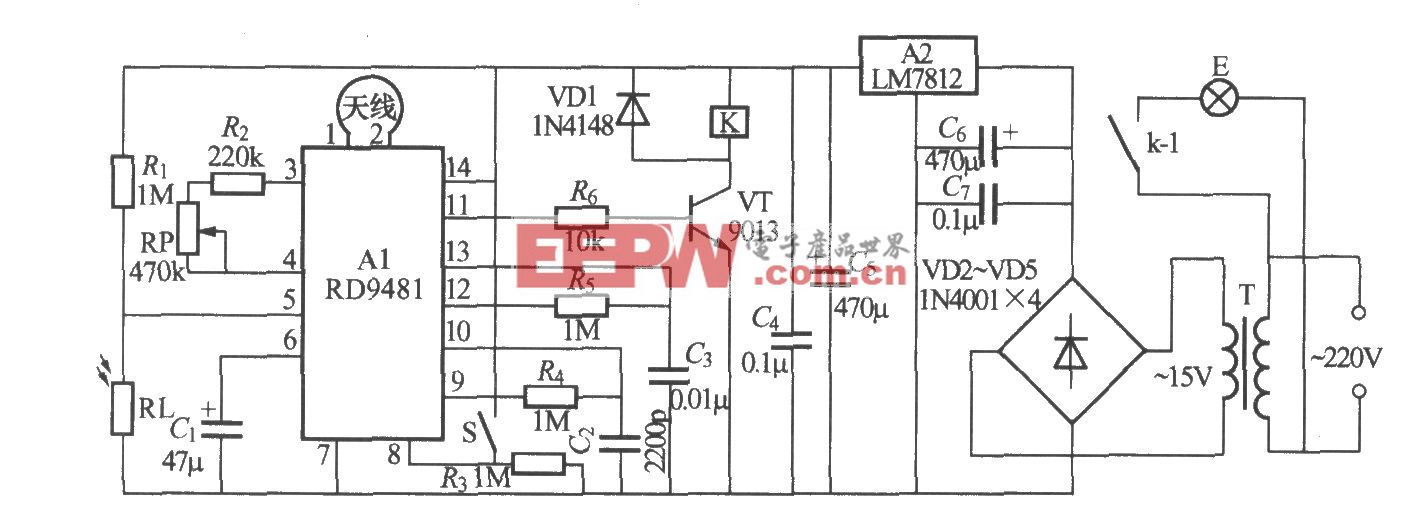

MERGE边界扫描扩展卡采用符合IEEE 1149.1边界扫描标准的可测试性设计方案,应用5片XILINX公司的XC95144芯片构建完整的从TDI至TDO的边界扫描链路,其中扫描链路的上游电路及下游电路采用74ACQ244对信号进行缓冲及整形,以增强上游电路的扇出能力,同时整板的边缘连接器采用了牢固可靠、抗腐蚀的欧式Eurocard结构形式的连接器,保证测试信号稳定、可靠。原理图如图 3所示。

JTAG-Control-PCI-USB控制器

JTAG-Control-PCI-USB控制器是测试系统笔记本记算机与被测试单元(BUT)进行信号控制的主要部件,实现工控机并行控制指令和数据向符合边界扫描测试协议的串行指令和数据的转换。电路采用DSP+CPLD的电路设计模式,DSP芯片采用TI公司的TMS320LF2407A,运行速度可高达40MIPS、具有至少544字的在片双访问存储器DARAM、2K大小的在片单访问存储器SARAM,32K的片内程序存储器FLASH;CPLD选用ALTERA公司的MAX7000S系列的EPM71285,其集成度为600~5000可用门、有32~256个宏单元和36~155个用户自定义I/O引脚、其3.3V的I/O电平与DSP芯片端口电平兼容、并可通过符合工业标准的I/O引脚JTAG接口实现在线编程及调试。JTAG-Control-PCI-USB控制器是PCI/IEEE 1149.1标准的主控单元,当与BS Interface Pod结合使用时,控制IEEE 1149.1标准自适应测试总线及与之相适应的离散信号。同时,该控制器还可控制施加到测试总线上负责JTAG-Control-PCI-USB控制器与BS Interface Pod进行通讯的低电压差分信号(基于TIA /EIA-644及IEEE 1596.3标准)。

评论