- Cadence设计系统公司宣布推出为半导体设计而准备的服务式软件(SaaS)。这些通过实际制造验证的、随时可用的设计环境,可以通过互联网访问,让设计团队可以迅速提高生产力,并降低风险和成本。Cadence Hosted Design Solutions可用于定制IC设计、逻辑设计、物理设计、高级低功耗、功能验证和数字实现。

Cadence Hosted Design Solutions通过提供集成的EDA软件套件以及相关的IT基础架构、计算、存储与安全网络功能,带来了一个完整的解决方案堆栈。&q

- 关键字:

Cadence 半导体 SaaS IC设计

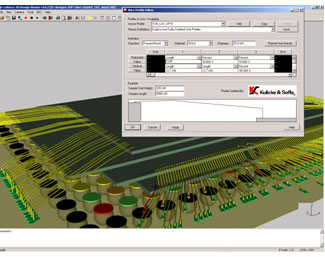

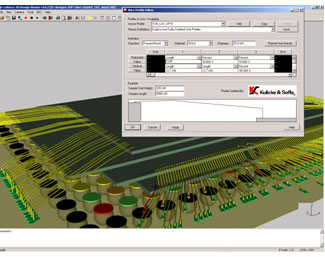

- Cadence设计系统公司近日发布了SPB 16.2版本,全力解决电流与新出现的芯片封装设计问题。这次的最新版本提供了高级IC封装/系统级封装(SiP)小型化、设计周期缩减和DFM驱动设计,以及一个全新的电源完整性建模解决方案。这些新功能可以提高从事单芯片和多芯片封装/SiP的数字、模拟、RF和混合信号IC封装设计师的效率。

设计团队将会看到,新规则和约束导向型自动化能力的推出,解决了高密度互连(HDI)衬底制造的设计方法学问题,而这对于小型化和提高功能密度来说是一个重要的促进因素,因而得以使总

- 关键字:

Cadence SPB 芯片封装 SiP

- Cadence发布了SPB 16.2版本,全力解决电流与新出现的芯片封装设计问题。这次的最新版本提供了高级IC封装/系统级封装(SiP)小型化、设计周期缩减和DFM驱动设计,以及一个全新的电源完整性建模解决方案。这些新功能可以提高从事单芯片和多芯片封装/SiP的数字、模拟、RF和混合信号IC封装设计师的效率。

设计团队将会看到,新规则和约束导向型自动化能力的推出,解决了高密度互连(HDI)衬底制造的设计方法学问题,而这对于小型化和提高功能密度来说是一个重要的促进因素,因而得以使总体的封装尺寸大大

- 关键字:

封装 设计 Cadence SPB

- 如果你问不同的人,会得出截然相反的结论。

几年前笔者参加过某EDA产品发布会后,咨询一家国内某微电子所的专家对此意见,他说:“一套新的设计工具要20万美元!相当于我们所一年的利润,而且这只是一个设计工具!”顿时,笔者为高科技即将造福我国设计业的兴奋劲儿被冷却了。

但是你去问EDA公司,他们的观点就不同了。最典型的,记得一家EDA厂商的老总说:你不要看一件东西本身的价格有多少,而要看它实际带来的价值有多大?如果你拿一个工具可以开发一个流行的产品,带来了100万美元的

- 关键字:

EDA Cadence IC设计业 居龙先生

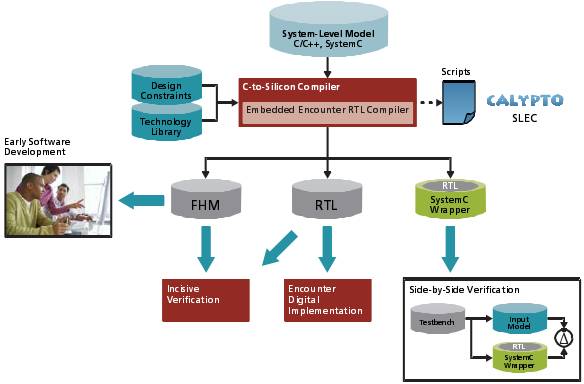

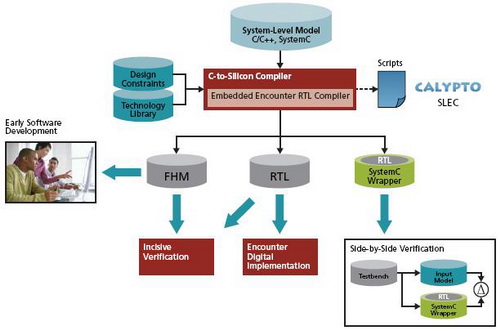

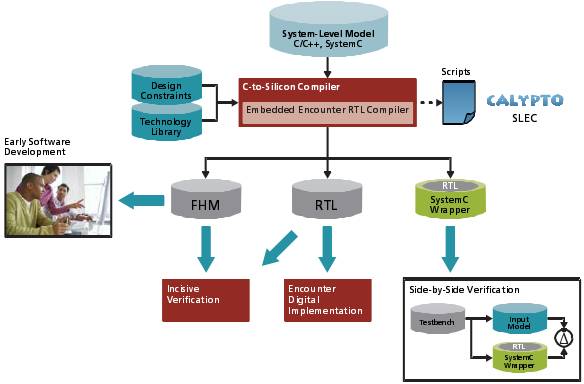

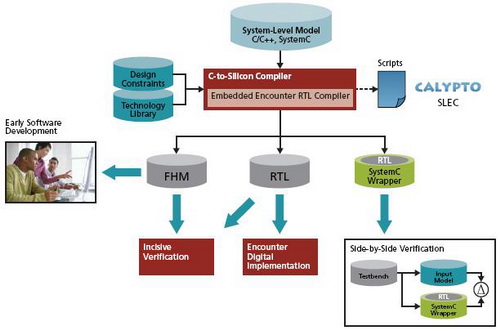

- 加州圣荷塞,2008年7月15日——全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种

- 关键字:

Cadence SoC C-to-Silicon Compiler 半导体

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种重要的新功能对于开发新型SoC和系统级IP,用于消费电子、无

- 关键字:

Cadence C-to-Silicon Compiler

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布推出Cadence® C-to-Silicon Compiler,这是一种高阶综合产品,能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁,它们通常是用C/C++ 和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种重要的新功能对于开发新型SoC和系统级IP,用于消费电子、无

- 关键字:

Cadence RTL SoC IP

- 全球电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布面向Common Platform™技术的45纳米参考流程将于2008年7月面向大众化推出。Cadence®与Common Platform技术公司包扩IBM、特许半导体制造公司和三星联合开发RTL-to-GDSII 45纳米流程,满足高级节点设计需要。该参考流程基于对应Common Power Format(CPF)的Cadence低功耗解决方案,而且还包含来自Cadence的关键可制造性设计(De

- 关键字:

CADENCE Common Platform ARM RTL-to-GDSII 低功耗

- Cadence设计系统公司宣布其多种领先技术已经纳入TSMC参考流程9.0版本中。这些可靠的能力帮助设计师使其产品更快地投入量产,提供了自动化的、前端到后端的流程,实现高良品率、省电型设计,面向晶圆厂的40纳米生产工艺。

Cadence已经在多代的工艺技术中与TSMC合作,开发参考流程,提供低功耗设计能力和高级DFM方法学。通过参考流程9.0,Cadence将这些性能拓展到该晶圆厂的40纳米工艺节点,使用光刻物理分析和强化的统计静态时序分析能力,此外一直追随TSMC参考流程的Cadence已经支

- 关键字:

Cadence 晶圆 设计 DFM 低功耗

- 全球电子设计创新企业Cadence设计系统公司(NASDAQ: CDNS)今天宣布其多种领先技术已经纳入TSMC参考流程9.0版本中。这些可靠的能力帮助设计师使其产品更快地投入量产,提供了自动化的、前端到后端的流程,实现高良品率、省电型设计,面向晶圆厂的40纳米生产工艺。

“TSMC和Cadence之间的合作提供了自动化的设计技术,这是在高级工艺节点上实现低风险和快速量产的必要技术,”TSMC设计基础架构营销部高级主管S.T. Juang说。

Cadence已经在多

- 关键字:

Cadence TSMC DFM

- 全球电子设计创新企业Cadence设计系统公司 (NASDAQ: CDNS)与领先的全球半导体晶圆厂UMC (NYSE: UMC, TSE: 2303)今天宣布推出基于通用功率格式(CPF)的低功耗参考设计流程,面向UMC 65纳米工艺。该参考流程让客户能够在使用UMC的低功耗套件时实现最佳的65纳米低功耗设计,该套件中包含了基于CPF的库和其他知识产权。

这种65纳米低功耗参考流程使用UMC的“Leon”测试芯片作为参考设计。Leon是一个开放源码的32位RISC微处理

- 关键字:

Cadence UMC 低功耗 Leon CPF

- 全球电子设计创新企业Cadence 设计系统公司(NASDAQ: CDNS)今天宣布推出首批两款对应开放式验证方法学(OVM)的高级测试平台验证IP(VIP)产品。这些改进能够让迅猛发展的OVM用户团体轻松获得Cadence®指标导向型验证解决方案,可预测地实现高质量验证闭合。AMBA® 3 AXI ™ 和AMBA AHB™ VIP已经在数百种设计中得以证明,现在作为多语言的通用验证组件(Universal Verification Components ,UV

- 关键字:

Cadence OVM 验证IP VIP

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天公布了一系列新的定制IC设计功能,帮助芯片制造商加快大型复杂设计的量产化,尤其是在65纳米及以下的高级节点工艺。这些经过实际生产证明对Virtuoso®技术的提升,进一步强化了Cadence用于降低风险和提升生产力的同时管理几何尺寸与复杂性的全套解决方案。

对Virtuoso® 定制设计平台的主要改进将会出现在最新版本中,提供更为紧密的可生产性整合、更好的寄生分析,更快的仿真工具,用于精确而高效地验证

- 关键字:

Cadence IC 定制数字 模拟/混合信号 系统级芯片设计 Virtuoso

- 全球电子设计创新领先企业Cadence设计系统公司(纳斯达克: CDNS),今天宣布Cadence®Virtuoso® Spectre® Circuit Simulator中的高级“turbo”技术目前已经推出,这是业界领先的模拟SPICE电路仿真器,获得了全面的晶圆厂支持。这种turbo技术能够在提升性能的同时,确保硅片的精确性,让设计师能够验证他们复杂的大型模拟设计,例如PLL(phase-locked loops)、ADC(analog-to-di

- 关键字:

Cadence turbo Cadence®Virtuoso® Spectre® Circuit Simulator

- 中国香港,2008年2月19日——全球电子设计创新领导厂商Cadence设计系统公司(纳斯达克: CDNS)今天宣布香港科技园公司(香港科技园)已经选择Cadence为其通信、无线、移动和多媒体产业的客户提供更先进的EDA技术和解决方案。通过与Cadence的合作,香港科技园帮助香港政府为众多中小型IC企业提供支持。此外,该合作关系再次确认了Cadence做为EDA供应商在香港的领先地位。

“通过我们与全球领先的EDA供应商Cadence的合作,香港IC设计平台已

- 关键字:

Cadence 香港科技园

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473