- 1. 赛灵思将在2013年7月10日宣布推出什么产品? 赛灵思宣布20nm两项新的行业第一,延续28nm工艺节点上一系列业界创新优势: middot; 赛灵思宣布开始投片半导体行业首款20nm器件以及投片PLD行业首款20nm All

- 关键字:

UltraScale ASIC 赛灵思 可编程

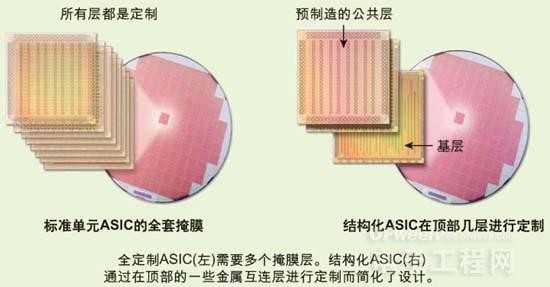

- 作为一个系统设计工程师,经常会遇到这个问题:是选用ASIC还是FPGA?让我们来看一看这两者有什么不同。所谓ASIC,是专用集成电路(Application Specific Integrated Circuit)的简称,电子产品中,应用非常广泛。ASIC的

- 关键字:

FPGA ASIC 系统设计 成本因素

- 我经常收到关于各类设备之间的差异的问题,诸如ASIC、ASSP、SoC和FPGA之间的区别问题。例如是SoC是ASIC吗?或ASIC是SoC吗?ASIC和ASSP之间的区别是什么?以及高端FPGA应该归类为SoC吗?这里有几个难题,至少技术和术语随

- 关键字:

ASIC ASSP SoC FPGA

- 联华电子今(12日)与ASIC设计服务暨IP研发销售厂商智原科技(Faraday Technology Corporation,TWSE:3035)共同发表智原科技于联电55奈米超低功耗製程(55ULP)的PowerSlash™基础IP方案。智原PowerSlash™与联电製程技术相互结合设计,为超低功耗的无线应用需求技术进行优化,满足无线物联网产品的电池长期寿命需求。

智原科技行销暨投资副总于德旬表示:「物联网应用建构过程中,效能往往受制于低功耗技术。而今透过联电55奈

- 关键字:

联华电子 ASIC

- 数字化是电子设计发展的必然趋势,EDA 技术综合了计算机技术、集成电路等在不断向前发展,给电子设计领域带来了一种全新的理念。本文笔者首先简

- 关键字:

EDA ASIC

- 本文通过列举Altera 公司的 20nm Arria 10 FPGA 和 Arria 10 SoC (片上系统) 开发电路板的电源管理解决方案,分析了对于FPGA、GPU 或 ASIC 控制的系统中电源管理带来的挑战,并指出通过使用 LTPowerCAD 和 LTPowerPlanner 这类工具,可以大大简化对负载点稳压器以及各部分分析结果的映射任务。

- 关键字:

电源管理 FPGA GPU ASIC 201609

- ASIC 设计服务暨 IP 研发销售领导厂商-智原科技(Faraday Technology, TAIEX: 3035)于日前获颁 ISO9001 Plus 典范奖项。ISO9001:2015是ISO 15年来最大改版,能成为首批获得SGS专业验证的厂商,是对智原在品质承诺、经营与职能发展表现上的高度肯定和最具体验证。

智原科技成立于1993年,累积20余年在 IP (矽智财)与 ASIC 设计服务的丰富经验,不但自主产出了3,000多支的 IP,更有2,000多个专案的成功量产经验,客户遍及台

- 关键字:

ASIC 智原科技

- 联华电子今(3日) 与 ASIC 设计服务暨 IP 研发销售厂商智原科技共同发表智原科技于联电28奈米 HPCU 工艺的可编程12.5Gbps SerDes PHY IP 方案。此次智原成功推出的 SerDes PHY,为联电28奈米 High-K / Metal Gate 后闸极技术工艺平台中一系列高速 I/O 解决方案的第一步。

藉由采用涵盖1.25Gbps 到12.5Gbps 的可编程架构技术,此 SerDes PHY 能够轻易支持10G/1G xPON 被动光纤网络通讯设备。结合不同的

- 关键字:

联华电子 ASIC

- 福建省晋江市举办了“国际集成电路产业发展高峰论坛”。在高端对话环节,部分企业家、协会领导、研发人员提出了发展内存/DRAM产业的思路和建议,对从较为落后的情况下赶超先进提供了启迪。

- 关键字:

内存 制造 晋华 201608

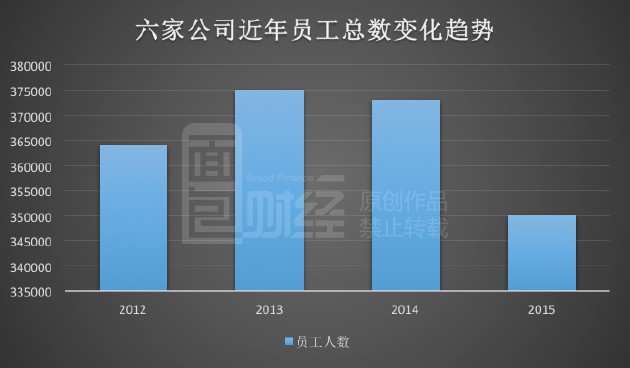

- 互联网与房地产烈火烹油,当制造业遭遇利润下滑压力的同时,资金正迅速被抽离,制造业正被冷落。

- 关键字:

制造 家电

- 传统的芯片销售方式是销售、现场应用工程师 (FAE) 介绍芯片会实现什么样的电性功能。但是对于客户来说, 这时芯片更像一个黑盒子,它具体是通过内部什么样的物理层架构得以实现外部的这些电性功能,客户并不十分了解。除此之外客户还关心产品在特定环境下的应用条件, 以及在此条件下的可靠性、一致性以及产品规模生产的可制造性。这就需要客户质量工程师(CQE)与客户沟通,了解到这些需求, 并通过对制造方法的控制,实现双赢。本文通过对Qorvo亚太区客户质量工程总监周寅的访谈,介绍了其RF、Filter等芯片的制程以及质

- 关键字:

IC 质量 制造 封装 测试 201605

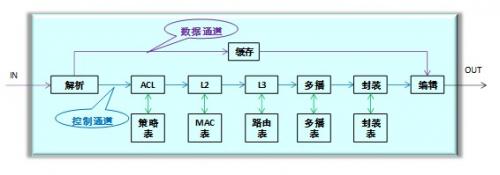

- 静态时序分析简称STA(Static Timming Analysis),它提供了一种针对大规模门级电路进行时序验证的有效方法。它指需要更具电路网表的拓扑,就可以检查电路设计中所有路径的时序特性,测试电路的覆盖率理论上可以达到100%,从而保证时序验证的完备性;同时由于不需要测试向量,所以STA验证所需时间远小于门级仿真时间。但是,静态时序分析也有自己的弱点,它无法验证电路功能的正确性,所以这一点必须由RTL级的功能仿真来保证,门级网表功能的正确性可以用门级仿真技术,也可以用后面讲到的形式验证技术。值

- 关键字:

fpga asic 静态时序

- 从2009年内蒙古3.6万吨垂直挤压机挤出第一根厚壁无缝钢管打破国外垄断,到2015年青海6.8万吨挤压和模锻双功能重型压机挤出世界第一长度的无缝钢管实现国际领先,短短几年技术创新突破,我国自主生产电力用高端耐热无缝钢管替代进口并跻身国际市场的夙愿正在成为现实。

“联手清华大学5年攻坚克难,世界首台6.8万吨重型压机能够完成95%以上的航空模锻件的生产,首根碳钢无缝钢管长达12.8米,直径630毫米,壁厚110毫米。”近日发布这一消息的青海康泰锻铸机械有限责任公司备受瞩目

- 关键字:

制造 无缝钢管

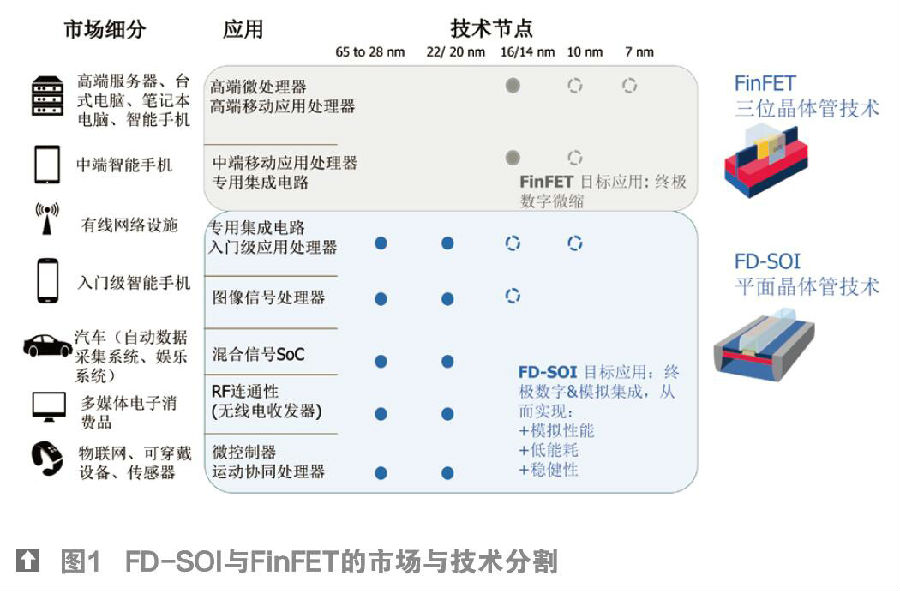

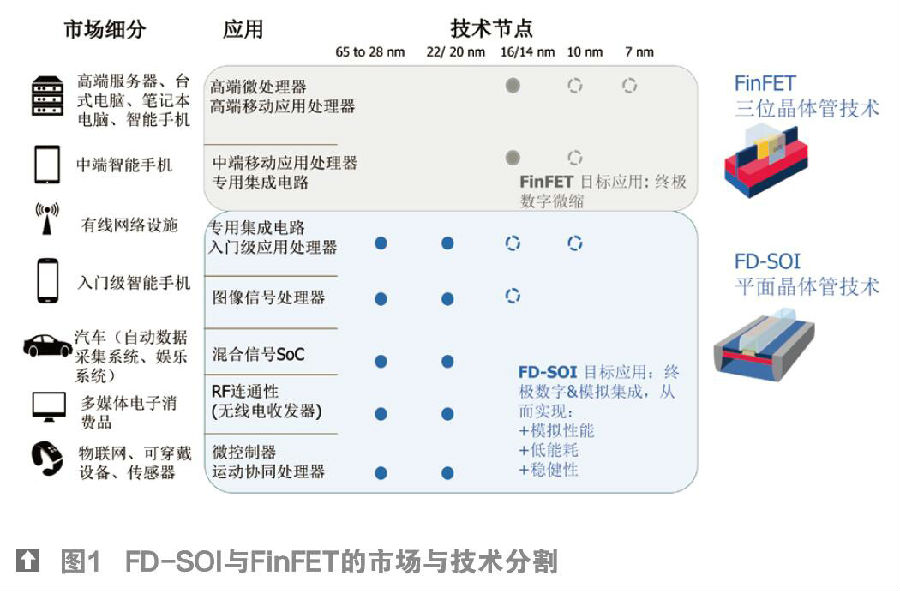

- 本文介绍了Soitec半导体公司的全耗尽绝缘硅(FD-SOI)的特点、最新进展及其生态系统,并将FD-SOI与FinFET作比较,分析了各自的优势、应用领域和应用前景。

- 关键字:

FD-SOI FinFET 制造 201604

asic 制造介绍

您好,目前还没有人创建词条asic 制造!

欢迎您创建该词条,阐述对asic 制造的理解,并与今后在此搜索asic 制造的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473