- 在我们大多数人“非黑即白”、“非此即彼”的观念里,半导体业者应该不是选择FinFET就是FD-SOI制程技术;不过既然像是台积电(TSMC)、GlobalFoundrie或三星(Samsung)等晶圆代工厂,必须要同时提供以上两种制程产能服务客户,有越来越多半导体制造商也正在考虑也致力提供“两全其美”的制程技术。

例如飞思卡尔半导体(Freescale Semiconductor)最近就透露,该公司正在14至16奈米节点采用

- 关键字:

FinFET FD-SOI

- GLOBALFOUNDRIES,世界先进半导体制造技术的领导者,今天宣布了其为14 nm FinFET工艺技术而开发的强化过的设计架构,在帮助那些采用先进工艺技术设计的客户的进程上达到了一个关键里程碑。

GLOBALFOUNDRIES与重要合作伙伴Cadence,Mentor Graphics,以及Synopsys合作开发出的新型设计流程,实现了从RTL到GDS的转换。该流程包括了基于工艺技术的PDK和早期试用标准单元库,形成一个数字设计“入门套件”,为设计人员进行物理实

- 关键字:

GLOBALFOUNDRIES FinFET

- 虽然台积电仍是全球晶圆代工市场的龙头大厂,但为牵就苹果(Apple)这个大客户,内部压宝16纳米、20纳米设备可以大部互通的产能扩充弹性优势,硬是将16纳米FinFET制程技术订为20纳米下一棒的规划蓝图。

反而在Altera、高通(Qualcomm)先后投入英特尔(Intel)及三星电子(Samsung Electronics)14纳米FinFET制程技术的怀抱后,即便苹果仍可喂饱台积电先进制程产能,但台积电客户结构从以IC设计公司为主,变成以系统厂独霸半遍天,加上主要竞争对手也开始争取到重要

- 关键字:

FinFET 晶圆

- Exynos 7420已经将与英特尔在2014年10月发表第一款14奈米Broadwell 处理器5Y70的差距缩小。

- 关键字:

三星 FinFET

- 亮点:

Galaxy Design Platform设计平台被用于90%的FinFET设计量产

强劲的平台采用率彰显了Synopsys在FinFET数字和定制设计实现工具领域内的领先性

所有的FinFET晶圆代工厂都已经使用并认证了Galaxy Design Platform

新思科技公司(Synopsys, Inc.,纳斯达克股票市场代码:SNPS)日前宣布:其 Galaxy™ Design Platform 设计平台支撑了90%基于FinFET设计的量产流

- 关键字:

Synopsys Galaxy FinFET

- 新思科技(Synopsys)宣布,Galaxy Design Platform已支援全球9成的FinFET晶片设计量产投片,目前已有超过20家业界领导厂商运用这个平台,成功完成超过100件FinFET投片。

格罗方德半导体(GLOBALFOUNDRIE)、英特尔晶圆代工(Intel Custom Foundry)、三星电子等晶圆厂已经利用Galaxy Design Platform为彼此之共同客户如Achronix、创意电子(Global Unichip Corporation)、海思半导体(H

- 关键字:

新思科技 FinFET

- 新思科技(Synopsys)近日宣布其 Galaxy Design Platform 已支援全球九成的 FinFET 晶片设计量产投片(production tapeout),目前已有超过20家业界领导厂商运用这个平台,成功完成超过100件FinFET投片。

包括格罗方德半导体(GLOBALFOUNDRIE)、英特尔晶圆代工(Intel Custom Foundry)、三星电子(Samsung)等晶圆厂已经利用Galaxy Design Platform为彼此之共同客户如Achronix、创意电

- 关键字:

Synopsys FinFET

- 联电积极扩充28奈米产能,预计今年中月产能可达2万片,28奈米毛利率将达平均水准。此外,联电已建置月产能约3,000片的14奈米生产线,预计第2季进行第2代14奈米鳍式场效电晶体(FinFET)制程试产,若下半年客户产品陆续完成设计定案(tape out),明年将开始拉升产能进入量产阶段。

联电去年第4季28奈米投片大增,包括高通、联发科等5家客户晶片进入量产,并有逾10家客户完成设计定案并展开试产,也让28奈米占去年第4季营收比重正式突破5%。联电已积极进行扩产,预估今年中可将28奈米月产能扩

- 关键字:

台积电 三星 FinFET

- 益华电脑(Cadence Design Systems)宣布,已与通讯网路与数位媒体晶片组供应商海思半导体(HiSilicon Technologies)已经签署合作协议,将于16奈米 FinFET 设计领域大幅扩增采用Cadence 数位与客制/类比流程,并于10奈米和7奈米制程的设计流程上密切合作。

海思半导体也广泛使用Cadence数位和客制/类比验证解决方案,并且已经取得Cadence DDR IP与Cadence 3D-IC 解决方案授权,将于矽中介层基底(silicon interp

- 关键字:

Cadence 海思 FinFET

- 三星电子(Samsung Electronics)在稍早传出开始量产采用14纳米FinFET制程技术的A9芯片,这对于三星来说,在抢佔先进微细制程市场以及与苹果(Apple)合作关系上,可以说是一箭双雕。

据ET News报导,三星美国奥斯汀厂传出已经开始量产采用14纳米FinFET技术的苹果A9。虽然美国奥斯汀厂以及韩国器兴厂均拥有FinFET制程的产线,但由于为量产的第一阶段,因此先由奥斯汀厂打头阵。

此外分析指出,由于顾及次世代芯片性能资安以及供应等问题,奥斯汀厂是在苹果的要求下首先

- 关键字:

三星 FinFET 14纳米

- 时间一晃又到了2014年的12月份,在辛苦工作了一年之后,大家都在等待着合家团圆,而IT行业也在酝酿着新的一年的改变。最新的消息是,AMD公司的“RedTeam”披露了其明年的APU和GPU规划,其中最引人注意的,自然是制程工艺的转变。然而外媒也指出,AMD的16纳米FinFET设计在2015年登陆主流市场并无望。

AMD首席技术官MarkPapermaster表示:“我公司的FinFET设计已经起步,但我们并不会是任何前沿技术的首个使用者”。换言

- 关键字:

AMD FinFET SoC

- 台积电昨(12)日宣布,完成16纳米主流制程FinFET+(鳍式场效晶体管强化版)全球首颗网通芯片及手机应用处理器试产,预定本月完成所有可靠性试验,明年7月正式量产。

这是台积电拓展先进制程一大里程碑。业界认为,正值三星再度与台积电争夺苹果下世代A9处理器订单之际,台积电16纳米FinFET+技术到位后,将进一步拉大与三星差距,对台积电而言,A9订单「有如探囊取物」,最快明年夏天开始投产A9芯片。

台积电昨天不对单一客户导入16纳米制程状况置评,强调明年底前,估计将完成近60件产品设计定案

- 关键字:

台积电 FinFET+

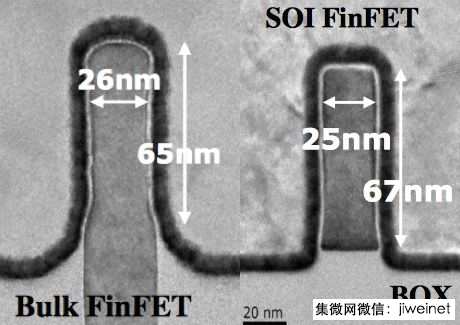

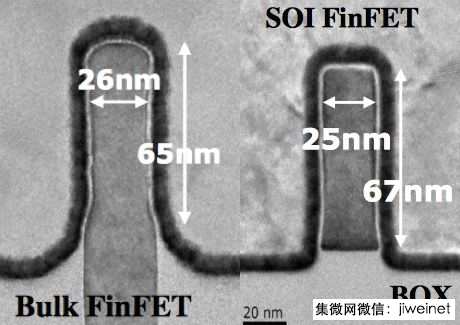

- 行动装置如智慧型手机、平板电脑等应用领域,对于半导体晶片的需求走到超低功耗,制程技术从28奈米制程,到20奈米制程,将于2015年进入第一代3D设计架构的FinFET制程,也就是14/16奈米世代。

台积电2015年下半即将量产16奈米世代,英特尔、三星电子(Samsung Electronics)、GlobalFoundries将是14奈米制程世代,英特尔早一些量产,之后是三星,GlobalFoundries制程技术将属于三星阵营。

台积电因为为大客户苹果生产20奈米制程晶片,因此16奈

- 关键字:

16纳米 FinFET

- 全球知名的电子设计创新领导者Cadence设计系统公司今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。该ULP平台涵盖了提供多种省电方式的多个工艺节点,以利于最新的移动和消费电子产品的低功耗需求。

为加速台积电超低功耗平台的技术发展,Cadence将包括存储器、接口及模拟功能的设计IP迁移到此平台。使用Cadence TensilicaÒ数据平面处理器,客户可以从超低功耗平台受益于各种低功耗DSP应用,包括影像、永远在线的语音、面部识

- 关键字:

Cadence 台积电 FinFET

- 全球知名的电子设计创新领导者Cadence设计系统公司今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。 Cadence所提供的丰富IP组合能使系统和芯片公司在16纳米FF+的先进制程上相比于16纳米FF工艺,获得同等功耗下15%的速度提升、或者同等速度下30%的功耗节约。

目前在开发16 FF+工艺的过程中,Cadence的IP产品组合包括了在开发先进制程系统单芯片中所需的多种高速协议,其中包括关键的内存、存储和高速互联标准。IP将在2014年第四季度初通过测试芯片测试。有关IP

- 关键字:

Cadence 台积电 FinFET

3nm finfet介绍

您好,目前还没有人创建词条3nm finfet!

欢迎您创建该词条,阐述对3nm finfet的理解,并与今后在此搜索3nm finfet的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473