- 数字供电和常见的模拟供电不同,前者采用了数字PWM,体积更小的整合了数字MOSFET和DRIVER的芯片,以及体积更小的 ...

- 关键字:

PWM IC 数字供电

- 9月6日德国柏林国际消费类电子展(IFA)正式拉卡帷幕。作为欧洲最大的电子消费展之一,IFA 2013可以说是今年诸多 ...

- 关键字:

IFA 3D 4K

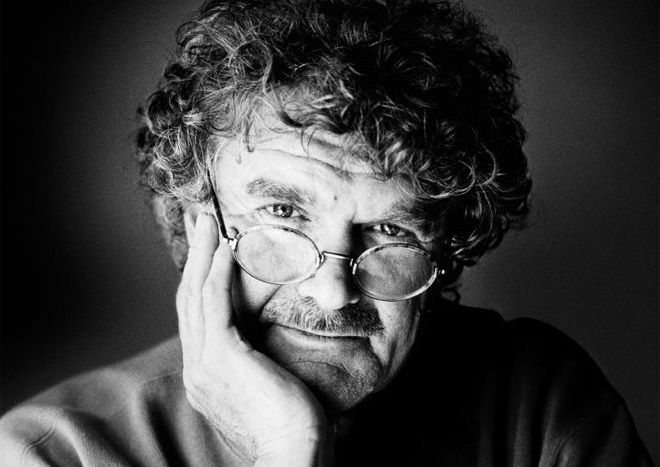

- Hartmut Esslinger是设计咨询公司Frog Design创始人,曾为苹果、微软、三星、索尼、LV、阿迪达斯等多家全球知名企业设计了经典产品。Hartmut Esslinger被《商业周刊》称为“自 1930 年以来美国最有影响力的工业设计师”。

- 关键字:

Hartmut 苹果 3D

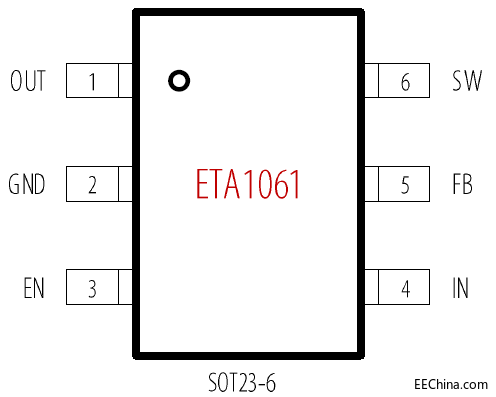

- 在LED照明领域,为体现出LED灯节能和长寿命的特点,正确选择LED驱动IC至关重要。没有好的驱动IC的匹配,LED照...

- 关键字:

LED 驱动 IC

- 从电源ic方案来看客户的基本需求,可以了解到,需求点会集中在对灯具系统进行保护,工作更安全,寿命更长方面。包括...

- 关键字:

电源 灯珠 ic

- OLED 屏幕分为被动矩阵 (PMOLED) 及主动矩阵 (AMOLED) 两种类型。PMOLED显示器的成本较低,也较易于生产制造。然 ...

- 关键字:

AMOLED 显示器 电源 IC

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布,台积电与Cadence合作开发出了3D-IC参考流程,该流程带有创新的真正3D堆叠。该流程通过基于Wide I/O接口的3D堆叠,在逻辑搭载存储器设计上进行了验证 ,可实现多块模的整合。

- 关键字:

Cadence 台积 3D-IC

- Mentor Graphics 公司(纳斯达克代码:MENT)日前宣布其解决方案已由台积电使用真正3D堆叠测试方法进行了验证,可用于台积电3D-IC参考流程。该流程将对硅中介层产品的支持扩展到也支持基于TSV的、堆叠的die设计。

- 关键字:

Mentor 3D-IC

- ? 新参考流程增强了CoWoSTM (chip-on-wafer-on-substrate)芯片设计

? 使用带3D堆叠的逻辑搭载存储器进行过流程验证

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)今天宣布,台积电与Cadence合作开发出了3D-IC参考流程,该流程带有创新的真正3D堆叠。该流程通过基于Wide I/O接口的3D堆叠,在逻辑搭载存储器设计上进行了验证 ,可实现多块模的整合。它将台积电的3D堆叠技术和Cadence?3D-IC解决方案相结合,包

- 关键字:

Cadence 3D-IC

- 全球3D设计、3D数字样机、产品全生命周期管理(PLM)解决方案和3D体验解决方案的领导者达索系统(Dassault Systèmes)(巴黎欧洲证券交易所:#13065, DSY.PA)今日发布了SOLIDWORKS® 2014 3D软件产品组合,涵盖了3D CAD、仿真、产品数据管理、技术沟通和电气设计,助力企业突破限制,实现更多创新设计。

全新发布的SOLIDWORKS 2014版本提供了卓越的生产效率和可用性,使得企业可以更专注于知识密集型任务,从而推动产品的创新。

- 关键字:

SOLIDWORKS 3D

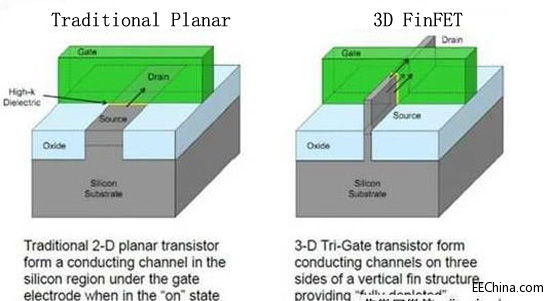

- 最近,“三维”一词在半导体领域出现得十分频繁。比如,英特尔采用22nm工艺制造的采用立体通道结构的“三维晶体管”、8月份三星电子宣布量产的“三维NAND闪存”,以及利用TSV(硅通孔)来层叠并连接半导体芯片的“三维LSI”等。

在半导体领域,原来的二维微细化(定标,Scaling)已逐步接近极限,各种三维技术变得十分必要。三维晶体管已广泛应用于微处理器,三维NAND闪存也有望在2014年以后、以服务器

- 关键字:

半导体 3D

- 3D视频拍摄 怎么样还原到人能看到的东西?通过两台摄像机,以前通过一台摄像机看到的是两维的,通过两台摄 ...

- 关键字:

3D 视频技术

- 电视的发展有两个很重要的趋势:从标清到高清的高清化,分辨率会越来越高;实现立体视觉体念的3D技术。特别是3 ...

- 关键字:

3D 视频技术

- “激水之疾,至于漂石者,势也”。现如今,“信息消费”的“势”已然到来。智能手机、平板电脑、智能电视、移动互联网以及相关的应用服务等新型信息消费高速发展,今年1至5月,中国信息消费规模已达1.38万亿元,预计到2015年总体规模将突破3.2万亿元,年均增长20%以上,带动相关行业新增产出超过1.2万亿元。信息消费领域成长的潜力正待无限释放。

正所谓信息消费、终端先行,而终端先行的先决条件离不开IC及传感器等的“鼎力

- 关键字:

IC 移动互联网

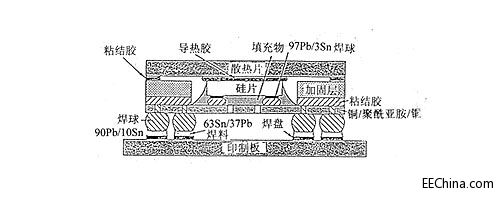

3d-ic介绍

3D IC产业链依制程可概略区分成3大技术主轴,分别是前段(Front-end)、中段(Middle-end)及后段(Backend)。前段制程涵盖芯片前段CMOS制程、晶圆穿孔、绝缘层(Isolation)、铜或钨电镀(Plating),由晶圆厂负责。为了日后芯片堆叠需求,TSV芯片必须经过晶圆研磨薄化(Wafer Thinning)、布线(RDL)、晶圆凸块等制程,称之为中段,可由晶圆厂或封测 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473