2.5D/3D 芯片技术将推动半导体封装技术的进步

来自日本东京科学研究所(Science Tokyo)的一组研究人员 conceptualised 一种创新的 2.5D/3D 芯片集成方法,称为 BBCube。

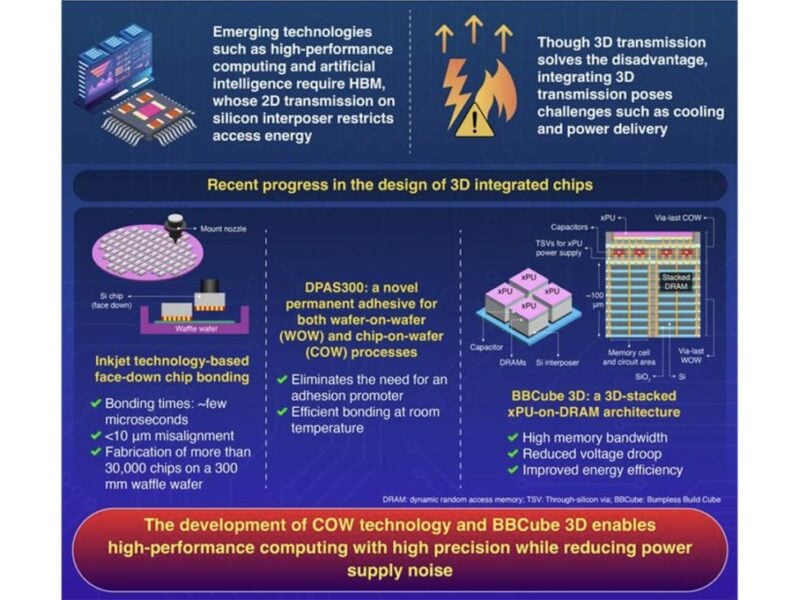

本文引用地址:https://www.eepw.com.cn/article/202506/471595.htm传统的系统级封装(SiP)方法,其中半导体芯片使用焊点排列在二维平面(2D)上,存在尺寸相关的限制,需要开发新的芯片集成技术。为了高性能计算,研究人员通过采用 3D 堆叠计算架构开发了一种新型电源技术,该架构由直接堆叠的动态随机存取存储器上放置的处理单元组成,这是 3D 芯片封装的重大进步。

为了实现 BBCube,研究人员开发了涉及精确和高速键合技术和粘合剂技术的关键技术。这些新技术可以帮助满足高性能计算应用的需求,这些应用需要高内存带宽和低功耗,并减少电源噪声。

该研究团队由小桥典雄教授、大庭隆之教授以及来自日本东京科学研究所(Science Tokyo)综合研究所的 WOW 联盟异构和功能集成部门的其他科学家组成,最初开发了一种倒装芯片-晶圆(COW)工艺,以规避使用焊料互连的限制。利用喷墨技术和选择性粘合涂层方法,他们成功地将不同尺寸的芯片依次粘合到晶圆间距为 10 微米、最小安装负载时间小于 10 毫秒的 300 毫米蛋挞状晶圆上。解释精确的 COW 工艺,小桥评论道:“在蛋挞状晶圆上制造了超过 30,000 个不同尺寸的芯片,实现了更高的粘合速度,且没有任何芯片脱落故障。”

为了实现精确高速的 COW 工艺,研究人员专注于解决影响超薄晶圆多层堆叠的热稳定性问题。通过精心设计化学特性,他们开发了一种新型粘合材料,称为“DPAS300”,该材料可用于 COW 和晶圆对晶圆工艺。这种新型粘合剂由有机-无机杂化结构组成,在实验研究中表现出良好的粘附性和耐热性。

最后,为了实现高内存带宽并提高 BBCube 的电源完整性,科学家们采用了一种由新型电源分配高速公路强化的 3D xPU-on-DRAM 架构。这包括在 xPU 和 DRAM 之间嵌入电容器,在晶圆上实施重分布层,以及在晶圆通道和 DRAM 刻线中放置硅通孔。乔指出:“这些创新将数据传输所需的能量减少到传统系统所需能量的五分之一到二十分之一,同时还将电源噪声抑制到 50 毫伏以下”,突出了 3D 堆叠计算架构的优势。

科研人员开发的东京科学 3D 芯片集成技术有可能改变下一代计算架构。

评论