Arrow Lake Die Shot展示了Intel 基于chiplet的设计细节

英特尔 Arrow Lake 架构的模具照片已经发布,展示了英特尔注入小芯片(tile)的设计的所有荣耀。X 上的 Andreas Schiling 分享了几张 Arrow Lake 的近距离图片,揭示了 Arrow Lake 各个图块的布局和计算图块内内核的布局。

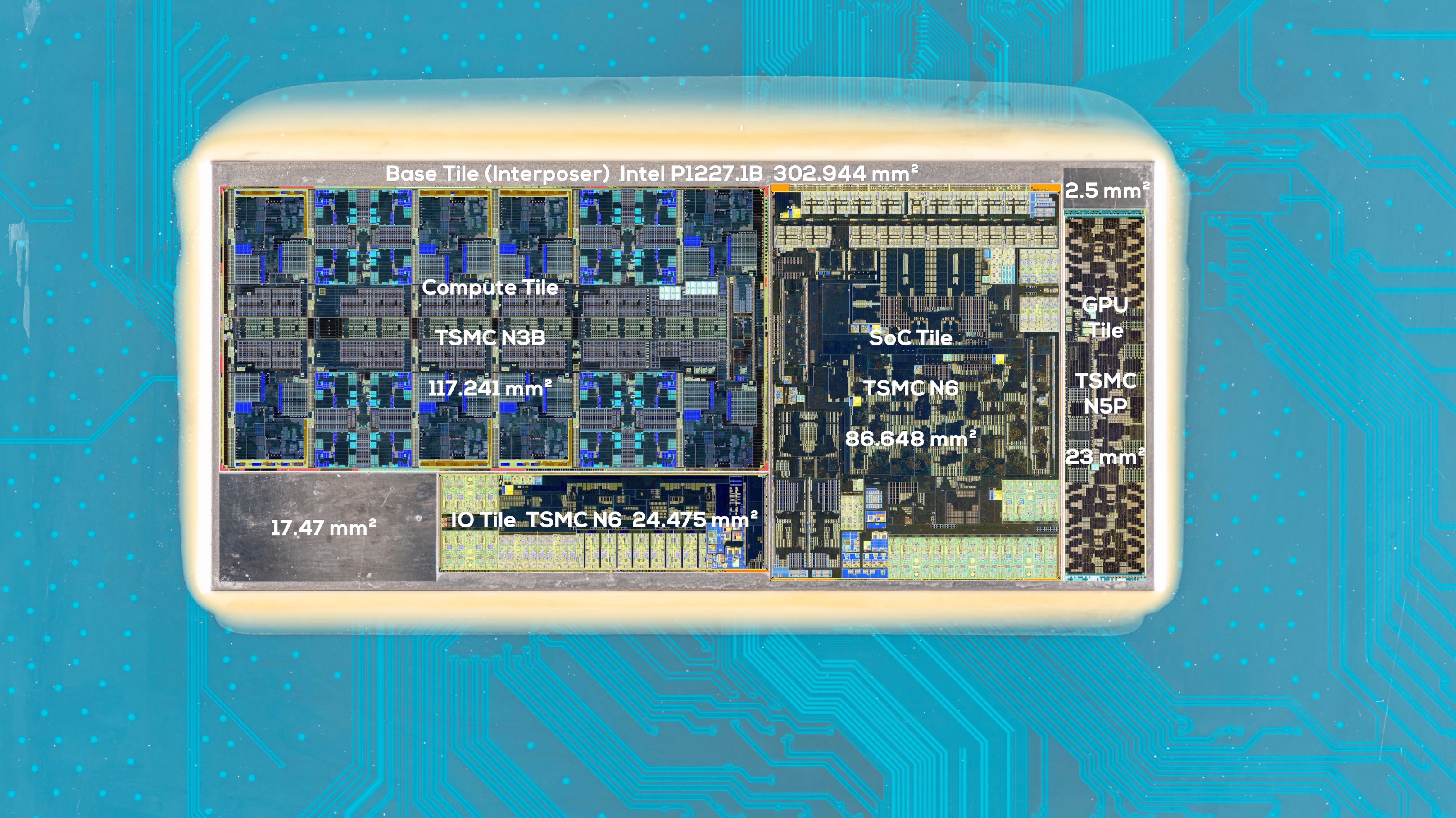

本文引用地址:https://www.eepw.com.cn/article/202505/470101.htm第一张照片展示了英特尔台式机酷睿 Ultra 200S 系列 CPU 的完整芯片,计算图块位于左上角,IO 图块位于底部,SoC 图块和 GPU 图块位于右侧。左下角和右上角是两个填充模具,旨在提供结构刚度。

计算芯片在 TSMC 的尖端 N3B 节点上制造,总面积为 117.241 mm²。IO tile 和 SoC tile 在台积电较旧的 N6 节点上制造,IO tile 的尺寸为 24.475 平方毫米,SoC tile 的尺寸为 86.648 平方毫米。所有 tile 都位于基于 Intel 22nm FinFET 节点的底层基础 tile 上。Arrow Lake 是第一个完全使用竞争对手的节点制造的 Intel 架构,但 base tile 除外。

下图显示了 Arrow Lake 中辅助图块的所有子组件。I/O 芯片容纳 Thunderbolt 4 控制器/显示器 PHY、PCIe Express 缓冲器/PHY 和 TBT4 PHY。SoC tile 包含显示引擎、媒体引擎、更多 PCIe PHY、缓冲区和 DDR5 内存控制器。GPU 图块包含四个 Xe GPU 内核和一个 Xe LPG (Arc Alchemist) 渲染切片。

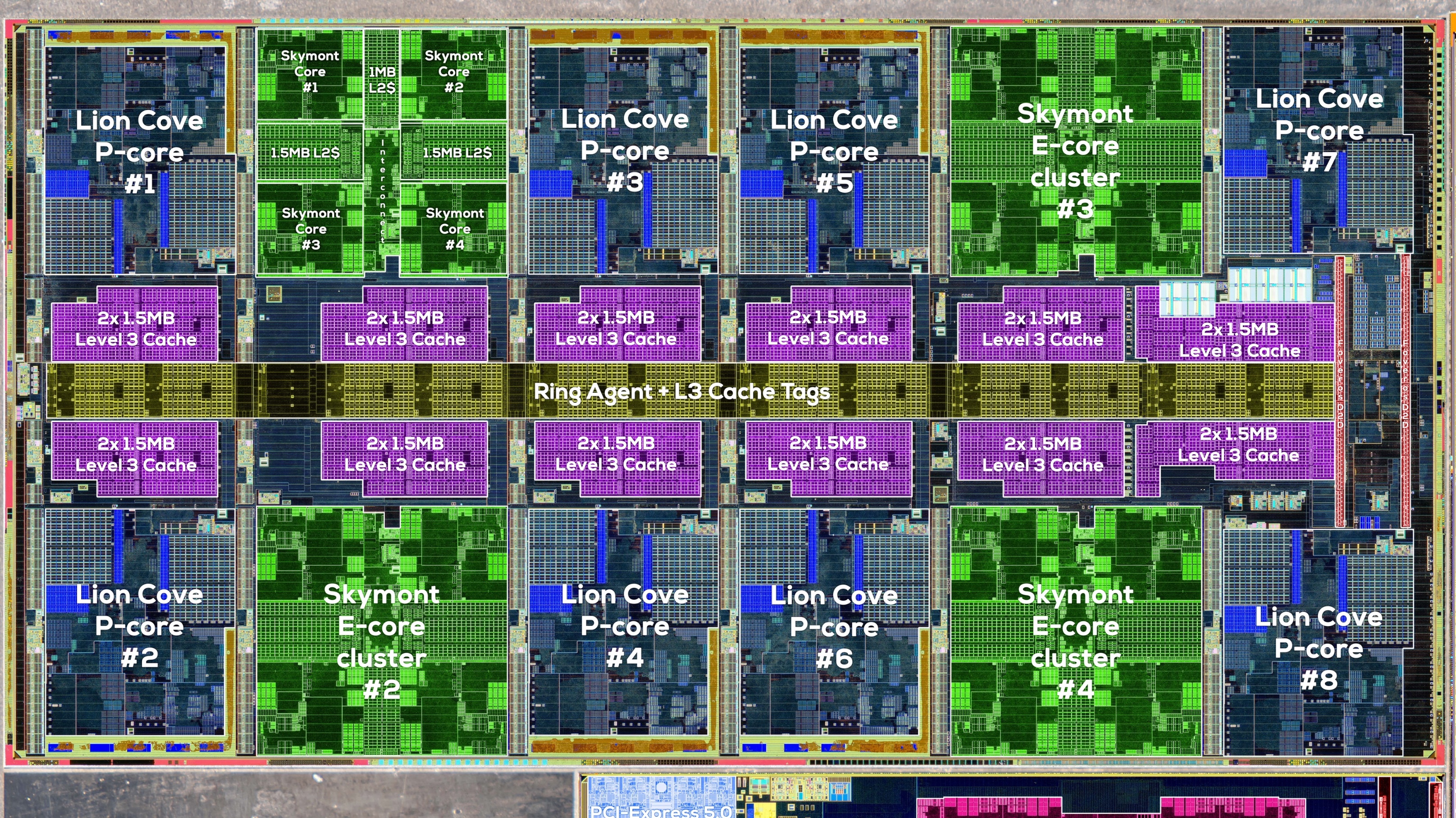

最后一张图片展示了 Intel 为 Arrow Lake 提供的最新内核配置,它与之前的混合 Intel 架构不同。对于 Arrow Lake,英特尔选择将 E 核夹在 P-core 之间,而不是将它们全部放在自己的集群中,据称是为了减少热热点。八个 P 核中有四个位于芯片的边界上,其他四个位于芯片的中间。四个 E 核集群(每个集群有四个内核)夹在外部和内部 P 核之间。

Schilling 的芯片还公开了 Arrow Lake 的缓存布局,包括每个 P 核心 3MB 的 L3 缓存(总共 36MB)和每个 E 核心集群 3MB 的 L2 缓存,其中 1.5MB 在两个内核之间直接共享。互连将两个 L2 缓存集群(及其关联的内核)桥接在一起,它还负责将每个内核集群连接到环形代理。英特尔对 Arrow Lake 进行的一项重大升级是将 E 核集群连接到 P 核共享的 L3 缓存,从而有效地为 E 核提供 L3 缓存。

Arrow Lake 是 Intel 迄今为止最复杂的架构之一,也是该公司第一个将小芯片式设计引入台式机市场的架构。也就是说,英特尔首次尝试基于台式机小芯片的竞争对手并未受到好评,因为互连的延迟问题,该互连负责将所有 tile 连接在一起。Intel 正在尝试通过固件更新来纠正此问题。尽管如此,它目前的实现无法触及 AMD 的竞争对手 Ryzen 9000 CPU(例如 9800X3D),甚至不足以击败自己的上一代第 14 代游戏处理器(例如 14900K)。

评论