台积电考虑推出大规模 1000W 级多芯片处理器,其性能是标准型号的 40 倍

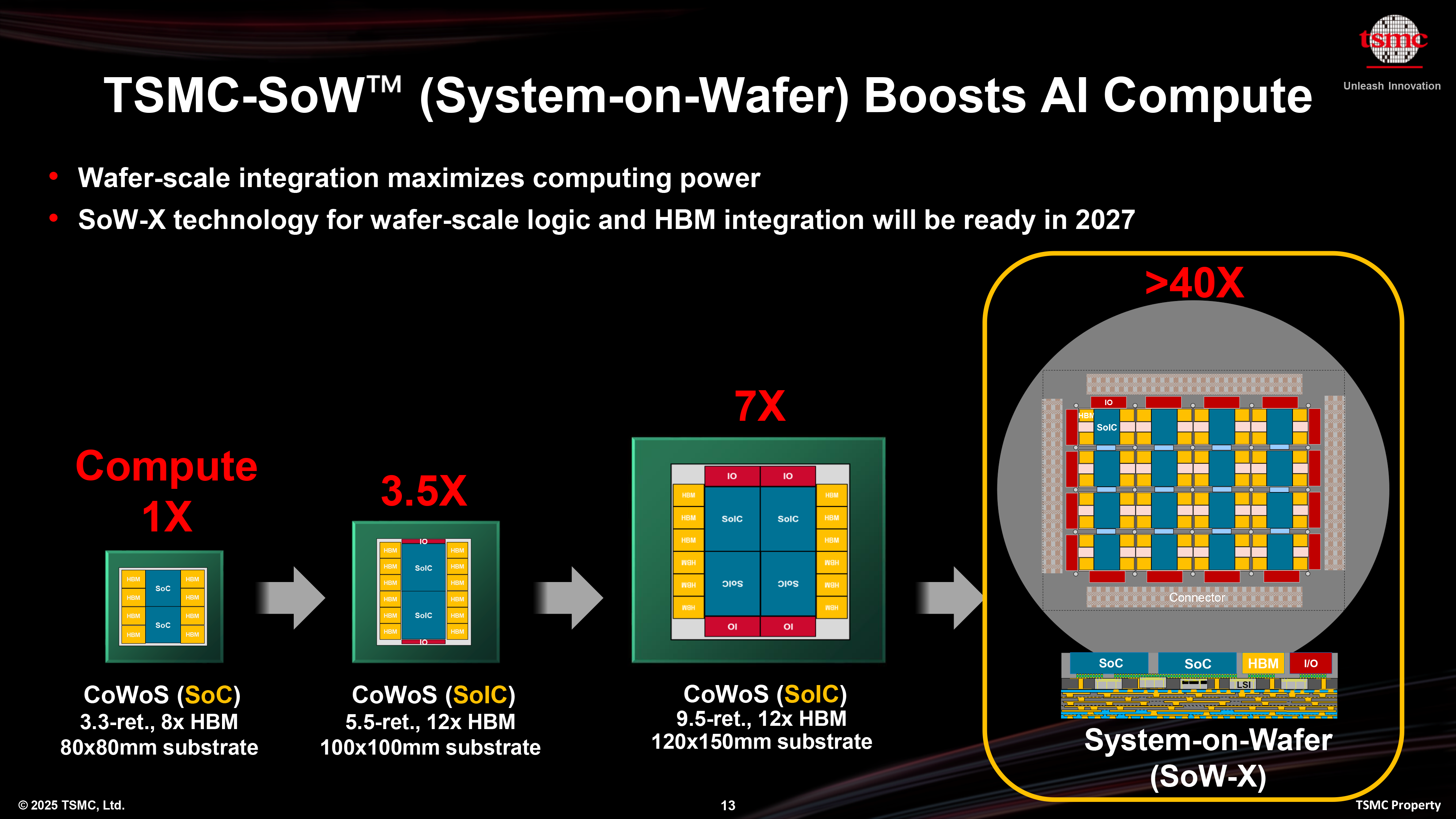

您可能经常认为处理器相对较小,但 TSMC 正在开发其 CoWoS 技术的一个版本,使其合作伙伴能够构建 9.5 个标线大小 (7,885 mm^2) 的多小芯片组件,并将依赖于 120×150 mm 的基板 (18,000 mm^2),这比 CD 盒的尺寸略大。台积电声称这些庞然大物可以提供高达标准处理器 40 倍的性能。

本文引用地址:https://www.eepw.com.cn/article/202504/469817.htm几乎所有现代高性能数据中心级处理器都使用多芯片设计,随着性能需求的提高,开发人员希望将更多的芯片集成到他们的产品中。

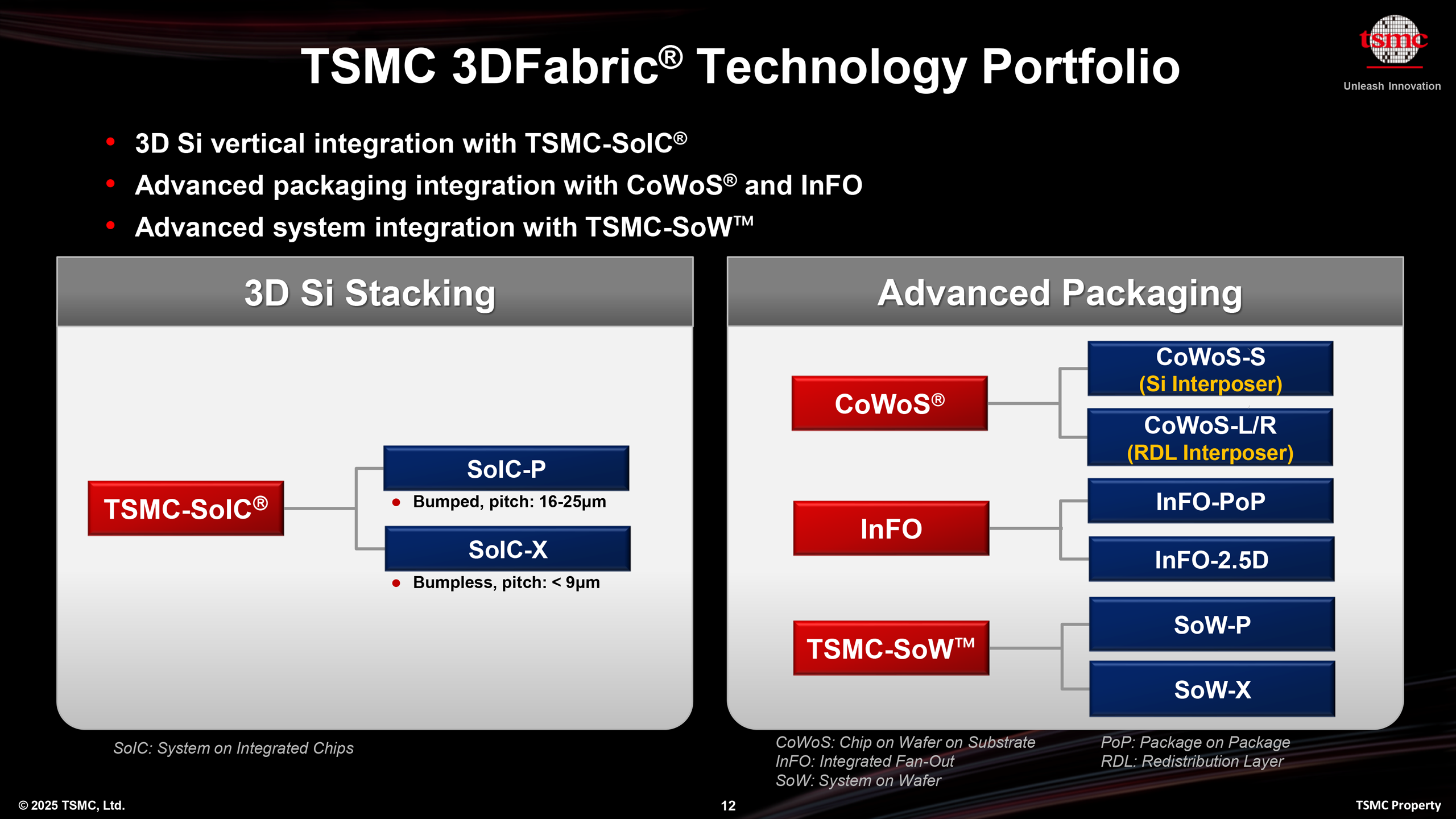

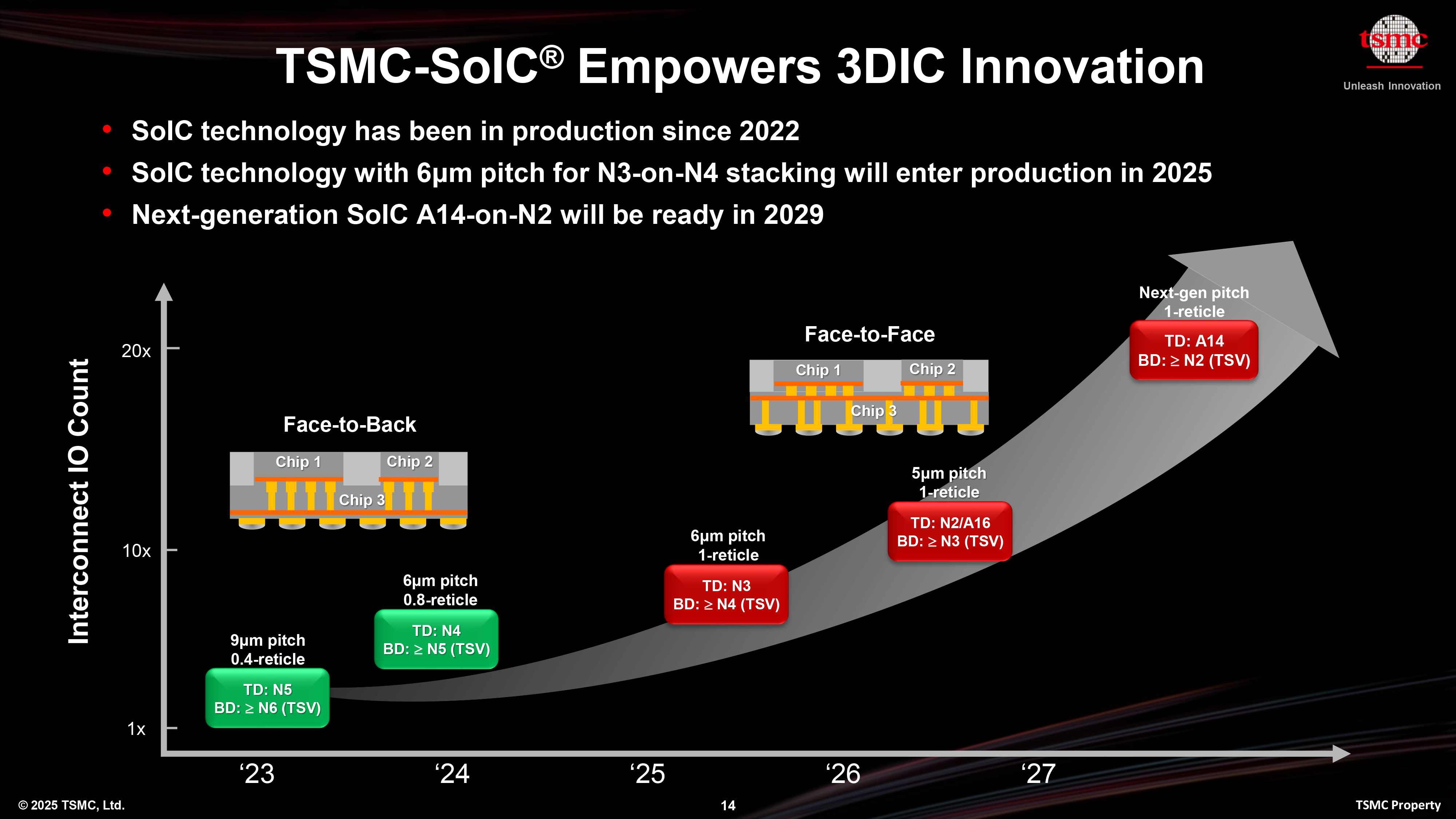

为了满足需求,台积电正在增强其封装能力,以支持用于高性能计算和 AI 应用的更大芯片组件。在北美技术研讨会上,台积电公布了其新的 3DFabric 路线图,该路线图旨在将中介层尺寸扩展到远超当前限制的程度。

从大到更大

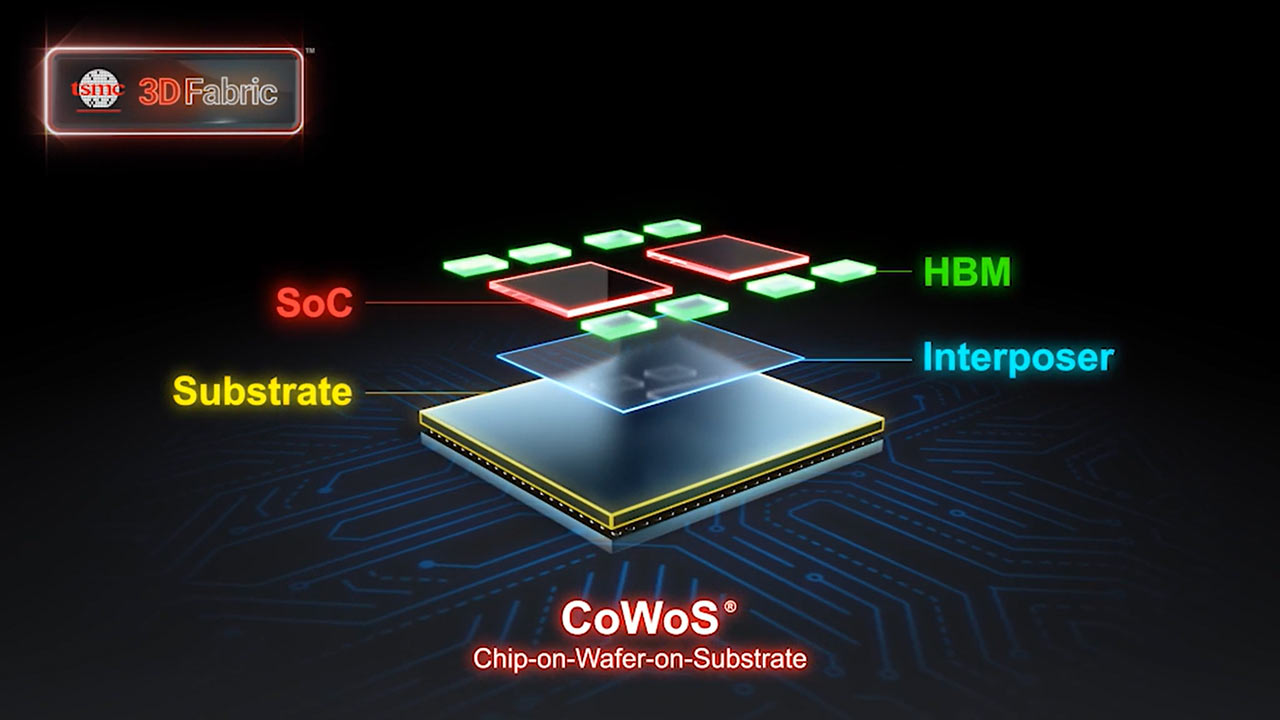

目前,TSMC CoWoS 提供的芯片封装解决方案可实现高达 2831 mm^2 的中介层尺寸,这大约是该公司的标线(光掩模)尺寸限制(根据 EUV 标准 858 mm^2,TSMC 使用 830 mm^2)的 3.3 倍。AMD 的 Instinct MI300X 加速器和 Nvidia 的 B200 GPU 等产品已经利用了这种容量,这些产品将两个用于计算的大型逻辑小芯片与八个 HBM3 或 HBM3E 内存堆栈相结合。但这对于未来的应用来说还不够。

(图片来源:台积电)

有时明年或稍晚,台积电计划推出其下一代 CoWoS-L 封装技术,该技术将支持尺寸高达 4,719 mm^2 的中介层,大约是标准标线面积的 5.5 倍。该封装最多可容纳 12 个高带宽内存堆栈,并且需要更大的基板,尺寸为 100×100 mm (10,000 mm^2)。该公司预计,基于这一代封装构建的解决方案将提供当前设计的三倍半以上的计算性能。虽然这种解决方案对于具有 12 个 HBM4 堆栈的 Nvidia Rubin GPU 来说可能就足够了,但提供更多计算能力的处理器将需要更多的芯片。

展望未来,台积电打算更积极地扩展这种封装方法。该公司计划提供面积高达 7,885 mm^2 的中介层,大约是光掩模极限的 9.5 倍,安装在 120×150 mm 的基板上(就上下文而言,标准 CD 珠宝盒的尺寸约为 142×125 mm)。

这比台积电去年在 120×120mm 基板上的 8 倍掩模大小的多小芯片组件有所增加,这种增加可能反映了代工厂客户的要求。这种封装预计将支持 4 个 3D 堆叠系统集成芯片(SoIC,例如,堆叠在 N3 逻辑芯片上的 N2/A16 芯片)、12 个 HBM4 内存堆栈和额外的输入/输出芯片(I/O 芯片)。

(图片来源:台积电)

但是,TSMC 的客户要求极致性能并愿意为此付费。对于他们,TSMC 提供了晶圆上系统 (SoW-X) 技术,可实现晶圆级集成。目前,只有 Cerebras 和 Tesla 的 WFE 和用于 AI 的 Dojo 处理器使用晶圆级集成,但台积电相信,除了这两家公司之外,还会有具有相似要求的客户。

评论