通过左移DRC设计规则检查方法降低IC设计复杂性

最成功的半导体公司都知道,集成电路 (IC) 设计日益复杂,这让我们的传统设计规则检查 (DRC) 方法不堪重负。迭代的“通过校正构建”方法适用于更简单的自定义布局,但现在却造成了大量的运行时和资源瓶颈,阻碍了设计团队有效验证其高级设计和满足紧迫的上市时间目标的能力。为了克服这种设计复杂性,主要半导体公司不断从其生态系统合作伙伴那里寻找有效的工具。西门子 EDA 是一家大型电子设计自动化 (EDA) 公司,它提供了一种新的、强大的左移验证策略,他们对其进行了评估并宣布它改变了他们早期设计阶段的游戏规则。

本文引用地址:https://www.eepw.com.cn/article/202503/467745.htm左移如何应对现代 IC 设计的挑战

电子行业不断发展,不断创新和改变集成电路的基本方面。整个生态系统都会做出反应并推动改进,从而产生更快、更小、更强大的 IC。对于制造前的物理设计和布局验证,我们曾经可以依靠手动的定制流程。这已经让位于高度自动化的工作流程和多层设计层次结构。由于不同的设计组件是由不同的设计团队在不同的时间表上开发的,因此要有一个完全组装的设计布局可用于全面验证变得极其困难。此外,当今高级工艺设计规则的庞大数量和复杂性加剧了制造前所需的关键设计规则检查 (DRC) 的运行时间和计算要求。

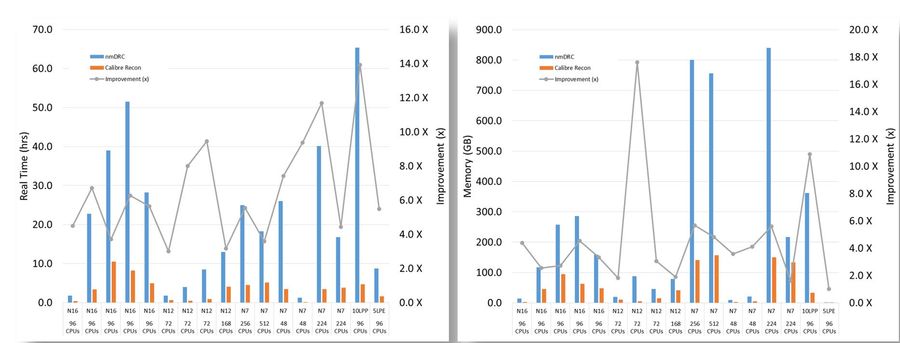

解决方案在于在设计过程的早期移动验证步骤——这种策略称为“左移”验证。通过将验证移至更接近设计更改源的位置,左移方法可以显著缩短调试时间,管理不完整的数据并加快流片路径。传统 DRC 运行和左移 DRC 运行之间的运行时间和内存差异很大,如图 1 所示。

图 1.与 Calibre nmDRC(蓝色条)相比,Calibre nmDRC Recon(橙色条)的运行时间和内存改进。西门子 EDA

图 1.与 Calibre nmDRC(蓝色条)相比,Calibre nmDRC Recon(橙色条)的运行时间和内存改进。西门子 EDA

主要半导体公司正在使用 Siemens EDA 的左移 DRC 工具(称为 Calibre DRC Recon)取得成功。该工具有效性的关键在于它能够仅识别和运行范围内的本地规则,而不是在整个设计中执行全面的 DRC 检查。与传统的 DRC 方法相比,这种“本地检查”方法大大降低了运行时和硬件要求。

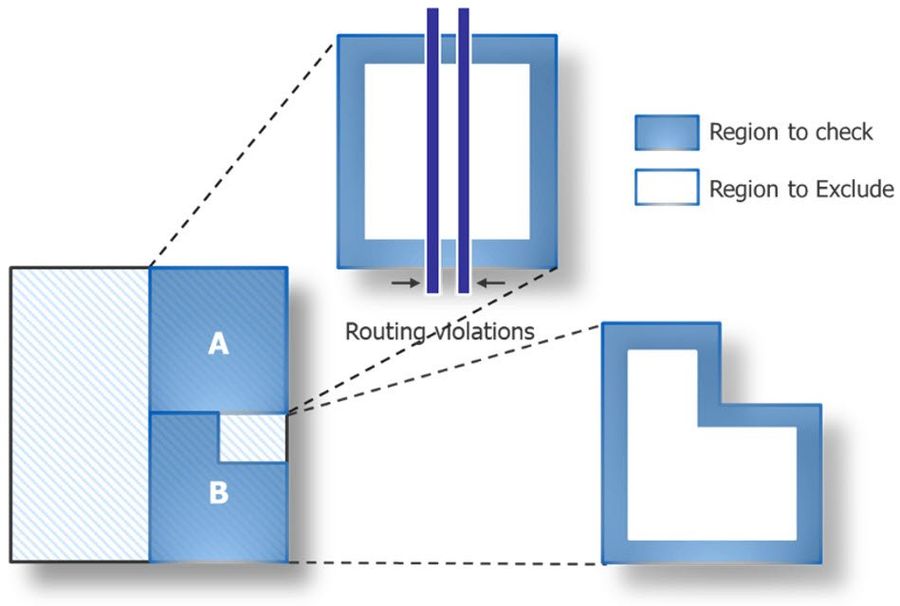

作为对本地检查方法的补充,设计人员还可以使用自动豁免功能来识别和排除设计中已知不完整的区域,从而消除它们进行检查,从而避免错误违规减慢验证过程。这是一种通过自动豁免实现的灰箱技术,如图 2 所示。

客户的左移 DRC 成功案例

一家领先的技术公司亲眼目睹了使用 Calibre DRC Recon 采用左移验证策略的好处。设计团队能够显著降低运行时和硬件要求,同时提高整体生产力。设计人员在平面图阶段开始使用 Calibre nmDRC Recon 迭代,然后在物理实现阶段。到那时,大多数设计都没有电源和接地网络的短路。他们能够及早发现任何问题,同时仍然很容易直接在布局环境中修复。由于这些修复是使用签核准确的 Calibre 规则进行的,因此团队知道结果是可靠且高度准确的。图 3 说明了不同 DRC 方法的运行时改进。

图 3.使用左移 DRC 时,运行时间显著缩短。西门子 EDA

图 3.使用左移 DRC 时,运行时间显著缩短。西门子 EDA

设计人员的经验展示了左移验证在实际应用中的强大功能。通过利用本地检查方法和互补功能(如自动豁免和分牌运行),该团队能够加快其设计迭代并缩短上市时间。

运行时的改进是显著的,与传统的 DRC 方法相比,左移 DRC 工具的性能提高了 15 倍。此外,内存使用量减少了 18 倍,使设计团队能够最大限度地提高其计算资源的利用率。

采用左移思维方式,加快 IC 设计速度

随着 IC 设计的复杂性不断升级,设计团队不能再依赖传统的 DRC 方法来跟上步伐。左移验证策略提供了一个引人注目的解决方案,可解决现代设计组织面临的关键挑战。

通过专注于本地检查、利用自动豁免和优化并行执行,左移 DRC 加快了设计和验证过程,简化了调试,并最终更快地将创新产品推向市场。该案例研究有力地证明了这种方法的变革性影响,突出了设计团队可以实现的显著生产力提升和效率提升。

对于希望保持领先地位的设计团队来说,采用左移思维方式进行物理验证至关重要。Siemens EDA 的先进 DRC 工具提供了一条行之有效的前进道路,使设计人员具备驾驭现代 IC 设计复杂性所需的能力,并以前所未有的速度和效率将其尖端产品推向市场。

评论