基于ARM的嵌入式语音存储系统设计

3.1 系统外围电路

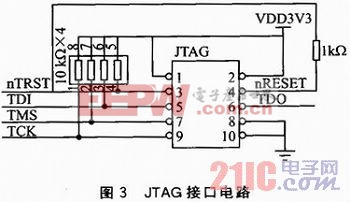

系统设计的外围电路都是ARM最小系统所必需的。电源电路为系统提供能量,是系统工作的基础。设计电源电路时要考虑的因素很多,主要包括输入及输出的电压范围、输出纹波大小、电池兼容和电磁干扰等,系统采用DC-DC转换芯片LM1117将5 V的电压转换成1.3 V、2.5 V、3.3 V后供系统使用。采用复位芯片MAX811产生的复位信号,既能保证上电复位的时间,又能保留手动复位的特点。时钟电路为系统提供工作时钟,主时钟采用12 MHz晶振作为时钟源,RTC时钟采用32.768 kHz晶振作为时钟源。通过JTAG接口,可以访问芯片内部的所有部件,是实现系统开发、调试的高效手段。为了减小系统体积,采用10针简化的JTAG接口,其接口电路如图3所示。

SDRAM存储器选择Samsung公司的K4S561632E-UC75,其存储容量为32 MB,具有存取速度快、成本低廉的特点,主要用来存放执行代码和变量,是系统启动之后主要进行存取操作的存储器。Flash存储器选择Samsung公司的K9F1208U0CNAND Flash存储器,其存储容量为64 MB,可以擦写一百多万次,具有很长的使用寿命,把启动程序、内核代码等固化到Flash闪存中能加速系统的启动、提高系统的稳定性和可靠性。

3.2 音频采集与处理模块

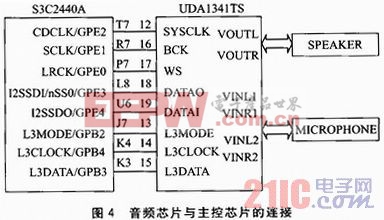

该模块采用Philips公司生产的音频芯片UDA1341TS,它支持I2S数据总线格式,且具有低功耗、低电压及DSP语音功能等特征。I2S(Inte grate Interfaceof sound)是Philips公司提出的串行数字音频总线协议,音频数据与控制信号、时钟信号分开传输,避免了由时钟带来的抖动问题,因此系统中可省略消除抖动的器件。

音频芯片与主控芯片的连接如图4所示。I2S音频接口包括5根信号线,其中音频模块的同步时钟CDCLK由S3C2440A提供,该时钟控制音频的A/D、D/A采样速率。串行时钟SCLK,也叫位时钟(BCLK),即每一个SCLK脉冲对应一位数字音频数据。帧时钟LRCK用于左有声道的切换,LRCK为1表示正在传输的是左声道的数据,为0则表示正在传输的是右声道的数据。DATAI是串行数据输入信号线,DATAO是串行数据输出信号线,所传输的音频数据用二进制补码表示。L3总线接口包括3根信号线:L3MODE/GPB2是微处理器接口模式信号线;L3CLOCK/GPB4是微处理器接口时钟信号线;L3DATA/GPB3是微处理器接口数据线。L3总线接口主要用于传输控制信号,相当于混音器控制接口,可以调节输入/输出音频信号的音量、低音提升、控制去加重等。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论