AM-OLED显示驱动芯片中内置SRAM的设计

仲裁器首先接受来自显示控制模块的SRAM读操作请求,然后接收来自MCU的写请求。这时,mcu_wr有一个上升沿,D触发器将锁存输出高电平,并经反相器反向输送到与非门,与非门输出低电平,使disp_r置“0”,以打断显示读信号响应,直到仲裁器处理完sram_wr信号请求,再由时序产生电路反馈一个完成信号sram_done,并清零sram_wr的D触发电路。由于显示读的D触发器的输出信号disp保持高电平,使与非门的输出变高,disp_r重新置为“1”,同时重新处理打断的disp_rd信号。

第二种时序冲突是仲裁器先收到外部MCU的读请求信号,在还没有结束处理这个请求信号时,显示控制模块的并行读请求信号已送到仲裁器。这时请求信号disp_rd的一个上升沿使disp由低电平变为高电平,此时mcu_rd的D触发器输出保持为高电平,与非门不受disp信号的影响,一直输出高电平。由于显示读请求信号被延迟,直到处理完MCU读请求信号,清零信号开启,使mcu_rd的D触发器输出低电平,这时,与非门输出高电平,disp_r重新置为“1”,时序产生电路响应其请求。

3.2 时序产生电路

由仲裁器电路产生的总请求信号sram_access送到这里后,可用以产生SRAM时序控制信号。该模块采用单稳态时序电路结构来实现其功能,其难点主要是解决预充信号Prech和字线选择信号WL的产生问题。根据SRAM的存储结构可知,Prech只在读操作才对位线充电,写操作时不充电;由于字线选择信号WL在读操作和写操作时的脉宽不一样,故需要采用不同时延模块,并根据不同操作,通过传输门来选择输出WL信号。

4 仿真结果

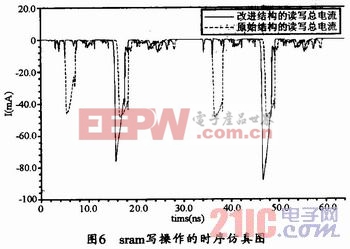

对基于0.18μm标准CMOS工艺库设计的大小为320x240x18位的内置SRAM结构使用Hspice对其子模块(320x60x18位)进行仿真,所得到的读写总电流波形如图6所示。本文引用地址:https://www.eepw.com.cn/article/166194.htm

由图6可见,改进结构在写操作时没有大电流,而在读操作时会有部分尖峰电流,这主要是由于平衡预充位线抬高了位线初始电压,从而降低了预充PMOS管的导通电阻所致。

改进SRAM结构的动态功耗为4.6mW。若用传统SRAM结构,对于相同大小的电路,其仿真得到的动态功耗为5.96mW。因此,相比传统结构,改进型结构的动态功耗减小了22.8%。

5 结束语

本文对显示驱动芯片中内置SRAM电路进行了低功耗研究与设计。新方法采用位线划分和字线划分技术来设计SRAM整体结构,从而降低了寄生电容。事实上,结合低功耗位线技术对传统SRAM单元结构进行改进,写操作时停止对位线预充电,可以达到降低功耗目的。而引入仲裁算法可解决SRAM访问的时序问题。根据SRAM读写操作要求设计的时序产生电路的仿真结果显示,其动态功耗可以得到大幅降低。

目前,本电路已经应用在一款AM_OLED显示驱动芯片中,并已完成前期仿真。仿真结果可以达到预期指标要求,从而证明了该电路的可行

性。

评论