基于电力网通信芯片的量产测试研究

1.3 ADC测试

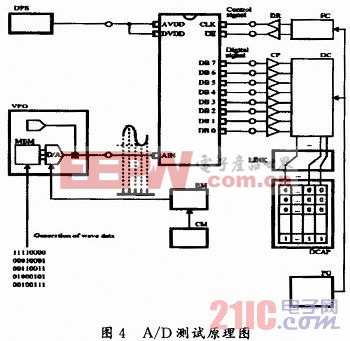

根据测试方案,使用ATE的模拟波形发生单元(HLFG)产生一频率约为132 kHz的正弦信号作为DUT的模拟输入,芯片的数字码输出由ATE的DCAP模块采样并保存在内存中。测试程序再对DCAP保存的数据进行FFT分析,计算得到SNR参数,并由SNR的值判断DUT是否通过A/D测试。

A/D测试原理如图4所示。本文引用地址:https://www.eepw.com.cn/article/155192.htm

DCAP在ADC测试中对芯片数字输出进行采样时需要一测试向量文件来控制其采样时间,主要为了等待HLFG模块稳定工作,以免DUT的输入不正确导致ADC测试故障。

1.4 D/A测试方法

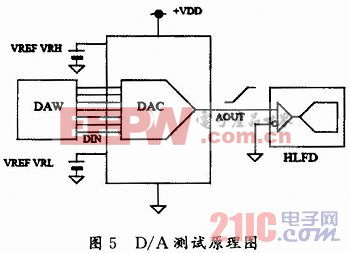

测试开发时用程序编写生成一数字序列作为DAC测试时的输入向量。按照测试方案该数字序列为2.5MHz采样132kHz信号,8比特量化。 ATE按照此向量文件产生8位数字信号作为待测DAC的输入,DUT的模拟输出被ATE的模拟波形采样模块(HLFD)采样。测试程序对HLFD采样结果进行FFT运算得到SNR参数,并由SNR的值判断DUT是否通过DAC测试。其D/A功能测试原理如图5所示。

2 程序调试及使用中的问题及解决方法

2.1 ADC测试中的时钟问题

在现场调试ADC测试程序时,程序运行完毕发现SNR为负值,用ATE的System view发现DCAP已经采样得到数据,且其频谱为一单频点(正弦信号)。

原因分析:从DCAP中数据的频谱来看,ADC输入信号为正弦,且采样得出了正弦序列。同时由于测试程序中是按132 kHz处的为信号来计算SNR的,所以可能的结果是计算程序的问题,或者HLFG模块产生的正弦信号不为132kHz。

使用示波器再次调试后发现,HLFG模块的实际输出频率为205 kHz,而时钟模块的输出时钟为3.9MHz,并不是预期的2.5MHz。在重新确认时钟模块连接、程序配置后,时钟恢复正常,ADC测试程序通过调试。

2.2 DAC测试的采样问题

DAC程序调试初期,ATE数字序列产生正确,DAC输出132 kHz模拟信号,但HLFD模块一直未能成功采样,采样结果全部为0。

通过查看手册和与ADVANTEST的工程师沟通,发现有两个问题:

(1)ATE测试程序一般是顺序执行,程序中是Pattern产生在前、HLFD采样在后,所以当HLFD开始采样时,数字序列已经不再产生,DAC也不会有输出;

(2)HLFD模块需要的采样时间较长,因为HLFD模块的数据并不是直接采样得到,而是反复采样后,计算恢复得到。

针对这两个问题,对测试程序做出修改:程序中强制让HLFD模块与Pattern发送并行进行,并将Pattern文件重复发送4次,以确保HLFD模块能完成采样。

修改后,HLFD模块正确采样,DAC测试程序通过调试。

2.3 四同测程序调试中的时钟模块问题

在四同测时,当芯片1测试失败,则其余芯片2、3、4的ADC、DAC测试均无法通过。

原因分析:如果芯片1测试失败进行错误处理时,ATE会给机械手(Handler)信息将芯片1分类至故障芯片,并在后续的测试项目中不对芯片1给出电源或信号。对于ATE而言,时钟模块的控制信号线与芯片的数字是无区别的,所以在芯片1测试失败后,ATE断开对时钟模块的控制信号,则时钟模块工作异常并导致ADC、DAC测试故障。

此问题有两种解决方法:一是在程序中先测芯片2、3、4,再测芯片1。这样的问题是会把四同测的测试时间增加一倍,实际上成为了二同测。方法二是ATE上引出四组时钟模拟控制信号,与进行或,这样只要有芯片还在进行测试,该组控制信号就可实现对时钟模块的正确配置,且无需增加测试时间,只需在时钟模块上加一部分或门电路即可。

2.4 生产测试过程中DAC的采样问题

程序调试完成后正式投入使用,一直工作稳定,在测试到第三批芯片时,DAC测试项目出现大范围的测试不通过。现象是大部分芯片的SNR都略低于通过门限,现象稳定。

原因分析:考虑到前两批芯片(约20 000片)一直测试正常,且此次测试未通过的芯片都是处于临界不通过的状态,所以初步猜想可能是在HLFD采样时DUT尚未完全稳定工作。通过分析DAC测试程序,在pattern发生开始后HLFD立即开始采样,可能此批芯片的稳定时间与前两批有异,所以导致DAC测试失败。在HLFD模块采样前加入10 ms延时保证DUT稳定工作,重新测试,故障问题解决。

3 测试成本压缩

成本的因素从头至尾影响着测试的开发。在制定测试方案时就考虑到测试成本的降低,当CP测试良率很高,以至于CP测试费用大于失效芯片的封装费用时,即可考虑取消CP测试,但在量产初期CP测试还起到给予晶圆厂信息反馈的目的。从芯片应用的反馈发现USER_ADC和USER _DAC几乎从未被使用,所以经过与系统集成商的沟通,在FT测试中取消了对USER_ADC和USER_DAC的测试,以降低测试成本。

进一步降低测试成本的方法还有对SCAN的测试故障结果进行分类,如果pattern的某些部分从未出错,在不影响测试结果的条件下,可考虑将部分pattern取消。

4 结论

随着集成电路的发展,芯片特征尺寸的降低与复杂度的提高对测试方法学产生了巨大影响,同时高速、数模混合的趋势对高性能ATE的需求带来了成本压力。本文首先讨论了数模混合芯片的常用测试方法,然后实现了基于爱德万T6575的测试开发及调试,并最终保证了该电力网通信芯片的顺利量产。本测试程序已在南通富士通封测厂实际测试出厂芯片逾百万片,保证了芯片品质,达到了预期设计要求。

评论