基于FPGA的可层叠组合式SoC原型系统设计

大规模SoC仿真验证手段有两种:一是采用专用的硬件加速器,另一种是采用FPGA原型进行系统逻辑验证。第一种方案的缺点在于只能加速特定的SoC设计,不具备通用性,而且价格昂贵。基于FPGA的SoC原型验证方法使用灵活、成本较低,目前被很多公司采用,已经成为SoC验证的最常用方式。目前大约2/3的SoC设计可以采用单FPGA原型,而另外1/3则需要多FPGA原型。因为这些超大规模SoC的设计逻辑量大大超出了目前最大FPGA芯片的容量,所以设计者必须对逻辑进行分割。分割后的多个模块分别加载到不同FPGA中,解决了单FPGA芯片容量不足的问题[2]。但是这种基于FPGA组的原型验证系统是由多片大容量FPGA构成的,成本高昂,不适合中小规模SoC设计,也不具备通用性。

本文设计了一种高度灵活的基于FPGA的可层叠组合式SoC原型验证系统。采用了模块化设计方法,通过创新性的互补连接器结构和JTAG控制电路设计,可支持1~5个原型模块的层叠组合。其中每个原型模块配备了500万门的FPGA,既可独立构成小型SoC验证系统,也可以层叠构成2 500万门的超大规模SoC验证系统。此外,原型模块通过USB2.0接口可以和PC主机交换数据,构成软/硬件协同验证系统[3]。本系统已成功应用于多款SoC芯片的验证,其中数字电视地面标准调制芯片BHDTMBT1006已经成功流片。

1 SoC原型模块设计

设计基于FPGA的SoC原型模块,需考虑的主要因素有FPGA的逻辑资源、速度等级、扩展能力、PCB信号质量以及易于调试等。其中,最重要的指标就是FPGA的逻辑资源。目前已经大批量生产的成熟FPGA芯片中,逻辑资源最大的是Altera公司的StratixII系列EP2S180,相当于500万逻辑门。对于SoC验证来说,稳定性和可靠性十分重要,因此原型模块的电路板结构和电路进行了特殊设计。

1.1 硬件系统设计

复杂的SoC设计一般都需要外围存储器,因此原型模块上配备了常用的储存器件。其中包括了DDRII SDRAM、Nand型和Nor型Flash芯片,这些就是嵌入式CPU所需要的外设资源。另外,可视化的调试工具对于芯片设计人员十分重要。在复杂SoC内部有大量的信号需要观察,传统的示波器和逻辑分析仪器很难满足信号数量的要求。因此,需要通过通用的接口,如USB、PCI等,在验证平台和PC机之间建立数据通信通道,用来观测各种信号。原型模块中采用了应用广泛的USB 2.0高速接口,并且设计了相应的软件,可以实现数据的采集和可视化测试。USB2.0接口被几乎所有的笔记本电脑厂家采用,因此本平台可以实现方便携带和移动,不依赖于台式机。为了实现层叠组合,原型模块采用了高度集成的电源系统和高速高密度连接器来实现小型化和高性能。另外,板卡采用全部工业级器件,可以直接应用于工业环境或者野外环境,满足了工业领域SoC和军品领域SoC的验证需要。

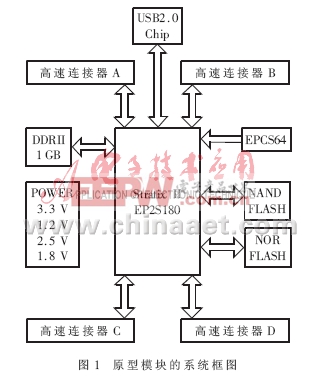

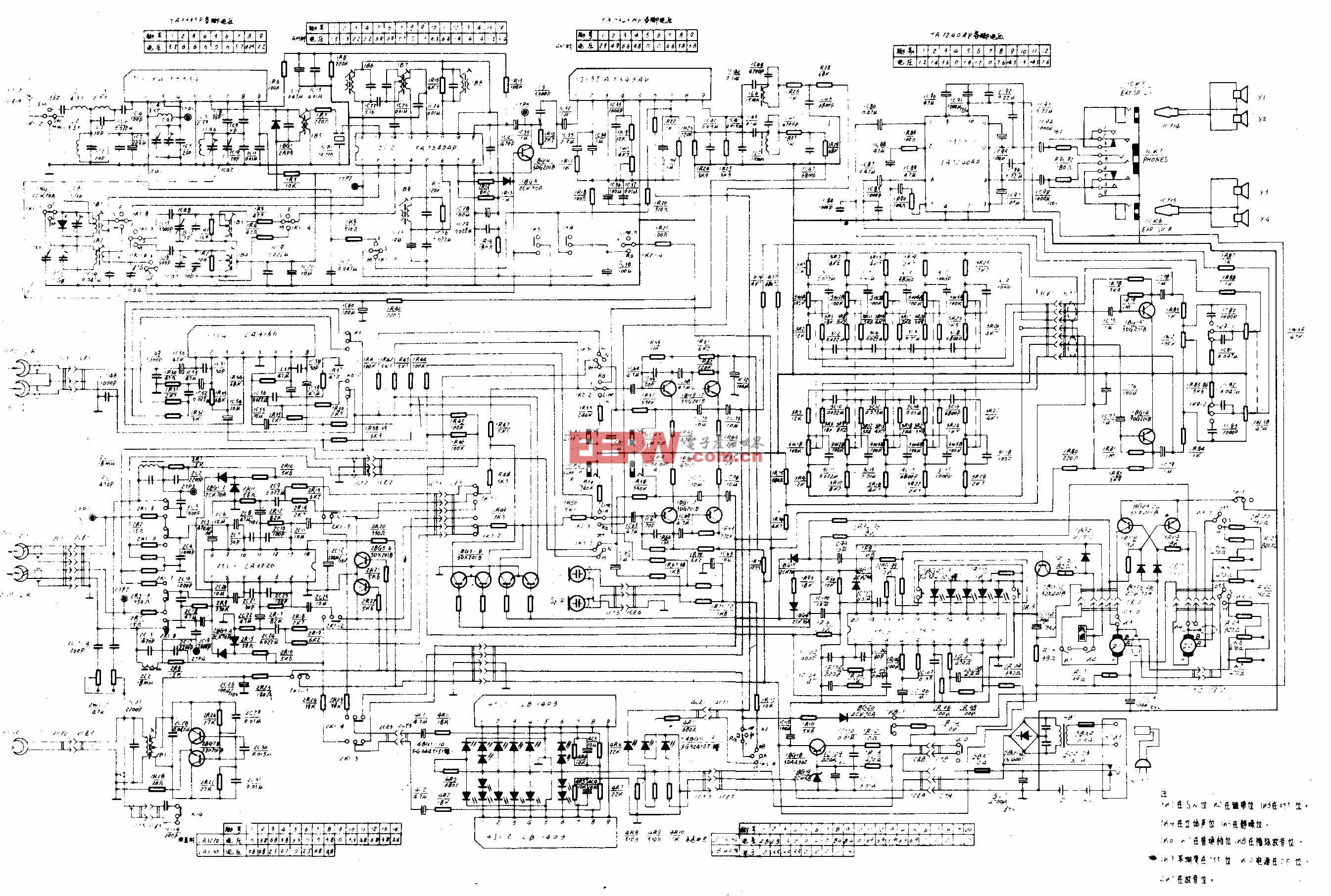

为了追求高性能,原型模块采用了12层PCB板精心设计,保证了信号完整性、速度以及一些关键的时钟路径。采用Cadence公司的PCB设计软件Allegro进行设计,采用SigXplore软件进行信号完整性分析。特别是4个高速连接的信号采用了等长处理和阻抗匹配,每个连接器的任意2个信号的延迟控制在50 ps范围内,保证了高速连接器的差分信号最高频率支持1 GHz,单端信号最高频率支持600 MHz。系统框图如图1。

1.2 互补连接器和JTAG控制器设计

高速连接器采用了SAMTEC公司的QSH/QTH系列高速差分连接器,最高频率支持8 GHz。高速连接器分成4组,每组由互补的两个连接器构成,其中一个置于板卡顶层(Top),另外一个放置于板卡相同位置的底层(Bottom),这样可以实现原型模块的垂直层叠。

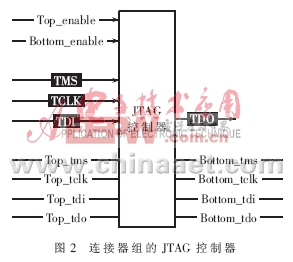

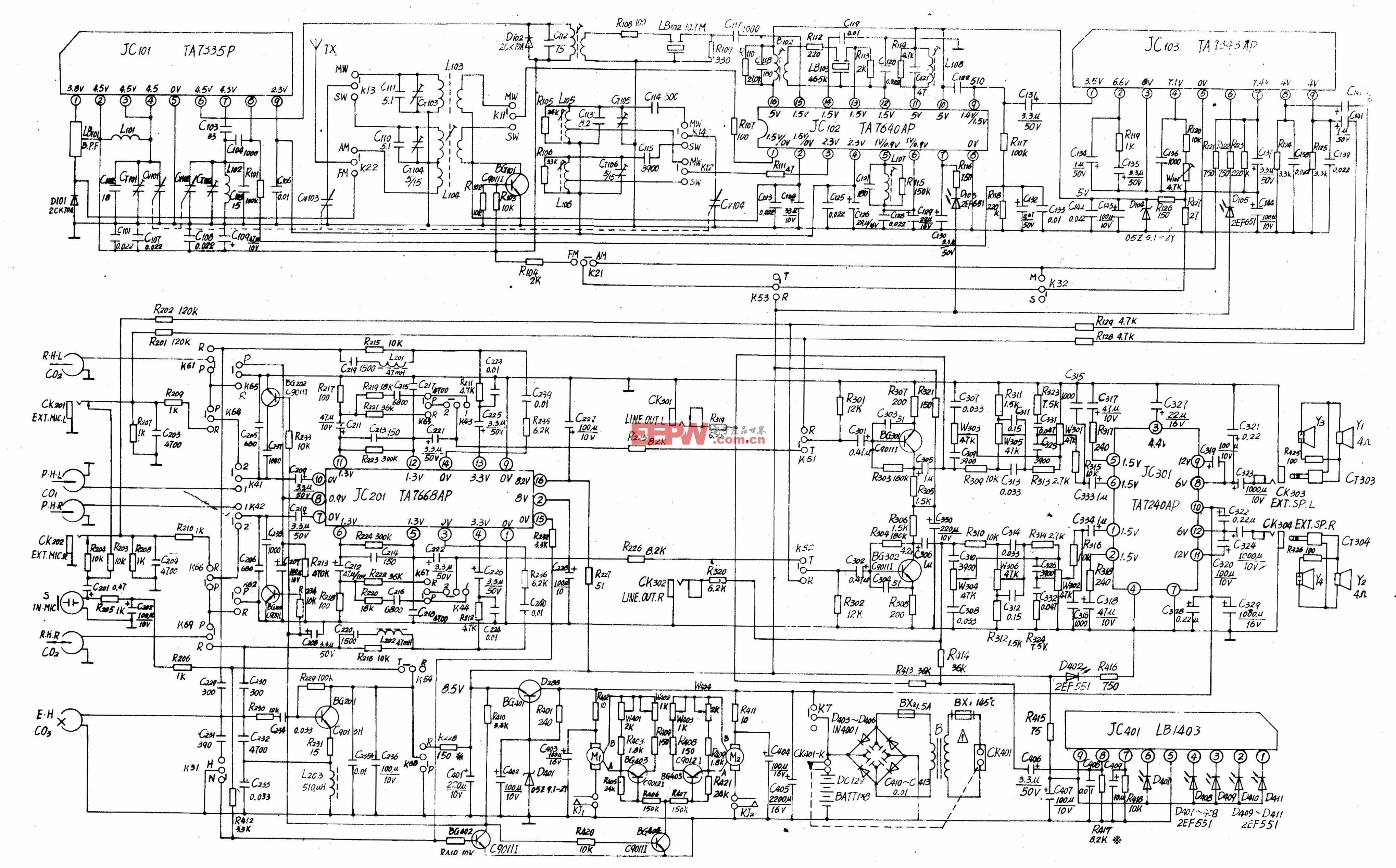

每个连接器都具有JTAG相关的管脚。顶层连接器JTAG相关的管脚为Top_tms、Top_tclk、Top_tdi和Top_tdo;底层连接器JTAG相关的管脚为Bottom_tms、Bottom_tclk、Bottom_tdi和Bottom_tdo。这一对互补连接器对外统一的JTAG信号定义为TMS、TCLK、TDI和TDO。这些信号的连接关系利用使能信号控制,顶层连接器上有板卡连接,Top_enable有效;底层连接器有板卡连接,则Bottom_enable有效。JTAG控制器的对外连接如图2所示。

评论