在ZVS拓扑中选择最优的死区时间

摘要:通过本文的分析来优化中压和高压功率MOSFET在各种隔离式转换器拓扑使用时的死区时间,能够帮助工程师发现各种器件技术的优点,甚至使那些过时的设计方案也能达到更好的性能。

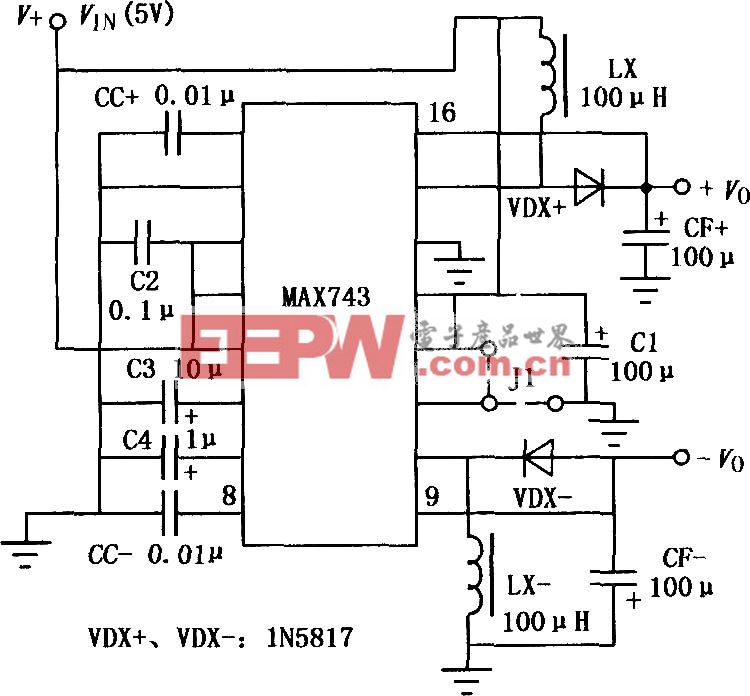

本文引用地址:https://www.eepw.com.cn/article/184600.htm中压和高压功率MOSFET在各种隔离式转换器拓扑中被广泛使用,例如半砖或全桥整流,以及单端升压或同步降压稳压器。桥式整流可以是硬开关或软开关,但目前的大多数转换器使用零电压开关(ZVS),避免导通时的开关损耗。功率部分是一样的,只是需要对器件开启和关闭的次序进行调整。在宽输入电压DC-DC砖式转换器里,同步降压转换器一般用于前端预稳压,在ZVS模式中还用来开关低边MOSFET。硬开关的桥式整流和升压转换器对死区时间没有严格的要求,所有的软开关ZVS桥式和同步降压转换器都必须在类似的限制条件下工作。在低压同步降压转换器中,在低边和高边MOSFET之间转换的死区时间由控制器或驱动器进行优化。还需要通过检测栅极驱动的下降沿或开关节点的电压,对器件采取防止共通的措施。此外,还有一些更加复杂的技术,设法能够连续地对延迟进行最优的调整。

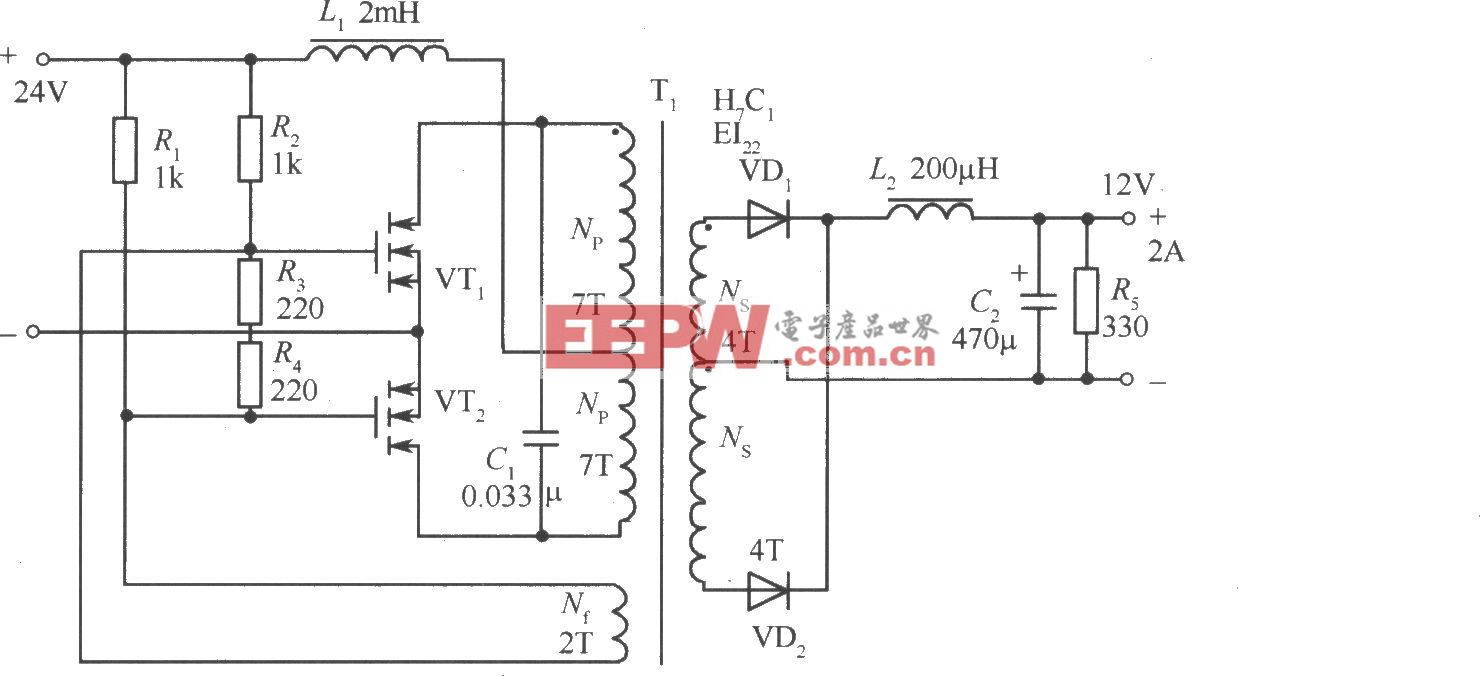

然而,像这样的精细调节对较高电压的驱动器并不实用,设计者必须回过头来在转换过程中采用固定的死区时间。由于长死区时间会导致体二极管的导通时间更长,进而损失效率,人们总是期望有一种办法,在不进入共通保护的条件下,能够提供优化的最小死区时间。这要求对整个转换过程有深入细致的了解,根据MOSFET和电路的参数,计算不同的时间间隔。当可以实现最优延迟,而且根据以往经验,这个条件是常常能够达到的,这时有必要对变化过程进行分析,选择能实现最高效率的合适器件。为说明这个分析过程,在本文中我们将使用一个软开关全桥整流,每个桥臂的满占空比为50%。这个拓扑也被称为直流变压器,在48V直流输入、非稳压中间总线转换器(IBC)输出的产品中用得比较普遍。在这里讨论的概念和参数折中也可以扩展到很多其他ZVS拓扑。

转换过程

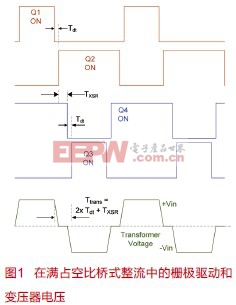

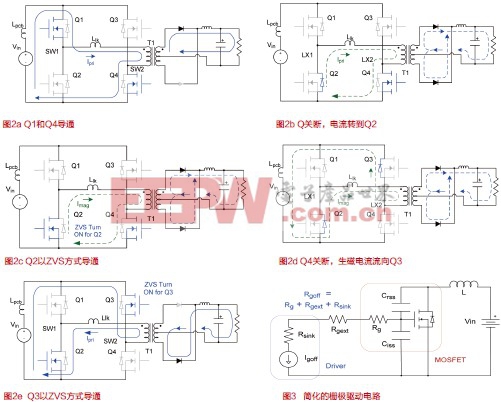

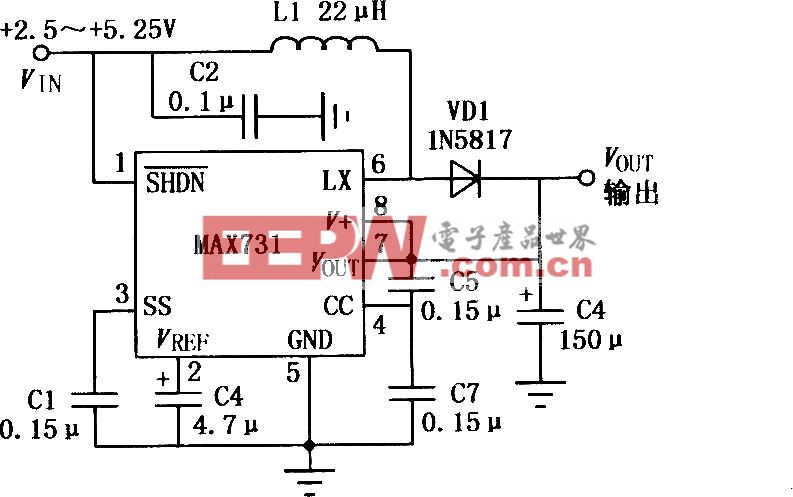

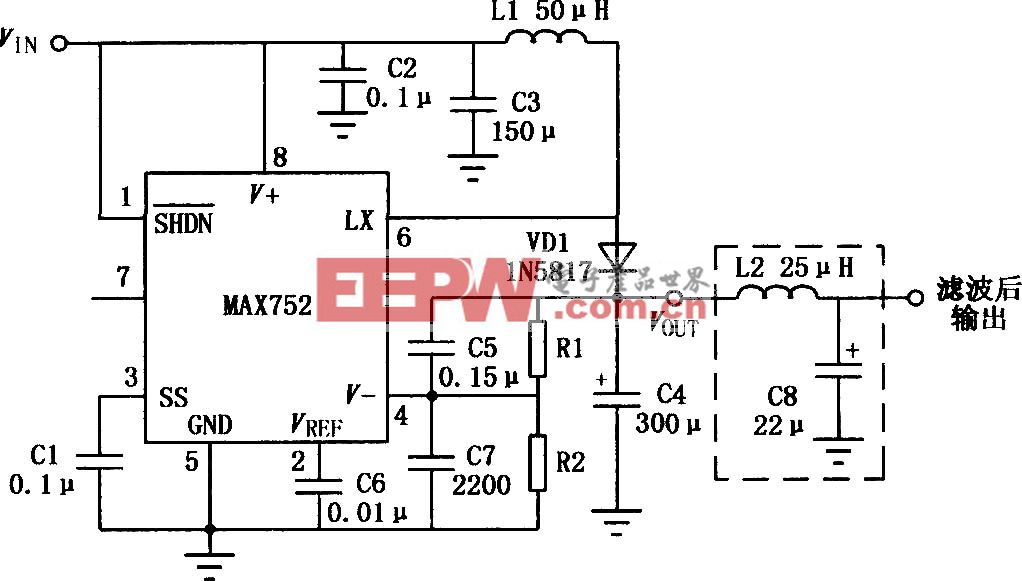

首先,软开关全桥整流的开关顺序有几种不同方式,每种都有其优点和缺陷。一个特别的顺序是,每个转换过程都是从关闭高边MOSFET开始,如图1所示。在转换过程中,流经不同器件的电流流向如图2a到图2e所示。开始阶段,Q1和Q4导通,能量输送到负载(图2a)。关闭Q1,开始转换,Q1的电流流向体二极管Q2(图2b)。间隔的持续时间是Tdt。

当Q完全关闭,Q2以零过流的方式导通。然后是很短的一段时间(TXSR),在这段时间里,变压器的初级侧对外短路,生磁电流在低边MOSFET(图2c)之间形成回路。在移相桥式转换器里,通过改变TXSR来实现输出稳压,但在直流变压器,要把TXSR保持在最小值。经过TXSR延迟后,Q4关闭,生磁电流流向Q3(图2d)。经过另一段时间间隔Tdt(图2e)后,Q3以ZVS方式导通,转换过程结束。

总转换时间的计算公式Ttrans = 2×Tdt + TXSR

间隔时间TXSR对初级转换并不重要,理论上这个时间可以为零。然而,次级同步整流器要求有一个最小的间隔时间。如果输出整流器被替换成同步MOSFET,其驱动信号在TXSR死区段内必须进行切换。不管是自驱动还是控制驱动的SSR,次级驱动脉冲在这两种情况下都要与初级侧相匹配。唯一的区别是,在自驱动方案中,TXSR要更高一些,因为变压器次级的上升和下降时间要长得多。要考虑的另一个因素是,从高边→低边和从低边→高边,转换过程是不对称的,因为由集成电路构成的栅极驱动在输入信号的电平转换过程中会增加延迟。这与正常的通过驱动级的传播延迟不同,是另外加上去的。从高边向低边转换过程中,电平转换延迟减少的可用死区时间甚至更多,但实际上对低边向高边转换有利,增加了可用的死区时间。大多数驱动会想办法把匹配的总延迟限制在几纳秒内,但是要把用TLSH表示的差值考虑进去。

评论