PWM芯片在开关电源中待机功能的设计实现

待机是指产品已连接到电源上,但处于未运行在其主要功能时的状态。待机的目的就是要降低电源在空载或轻载时的损耗。这可以通过许多控制功能芯片来实现,例如集成芯片L5991等。目前,很多PWM芯片还不具有变频的待机功能,因而,我们可以借鉴L5991芯片的这个功能电路来实现其他PWM芯片的待机功能。

本文引用地址:https://www.eepw.com.cn/article/180672.htm2 L5991芯片的待机功能电路介绍

L5991芯片,是由BCD60II技术发展而来的,设计目的是用一个固定频率的电流模式控制,实现离线式DC/DC电源应用。L5991是一个标准电流型PWM控制器,该控制器具有可编程软启动,输出/输入同步,闭锁(用于过压保护和电源管理),精确的极限占空比控制,脉冲电流限制,用软启动来进行过流保护,和当空载或轻载时使振荡器频率降低的待机功能等优点。

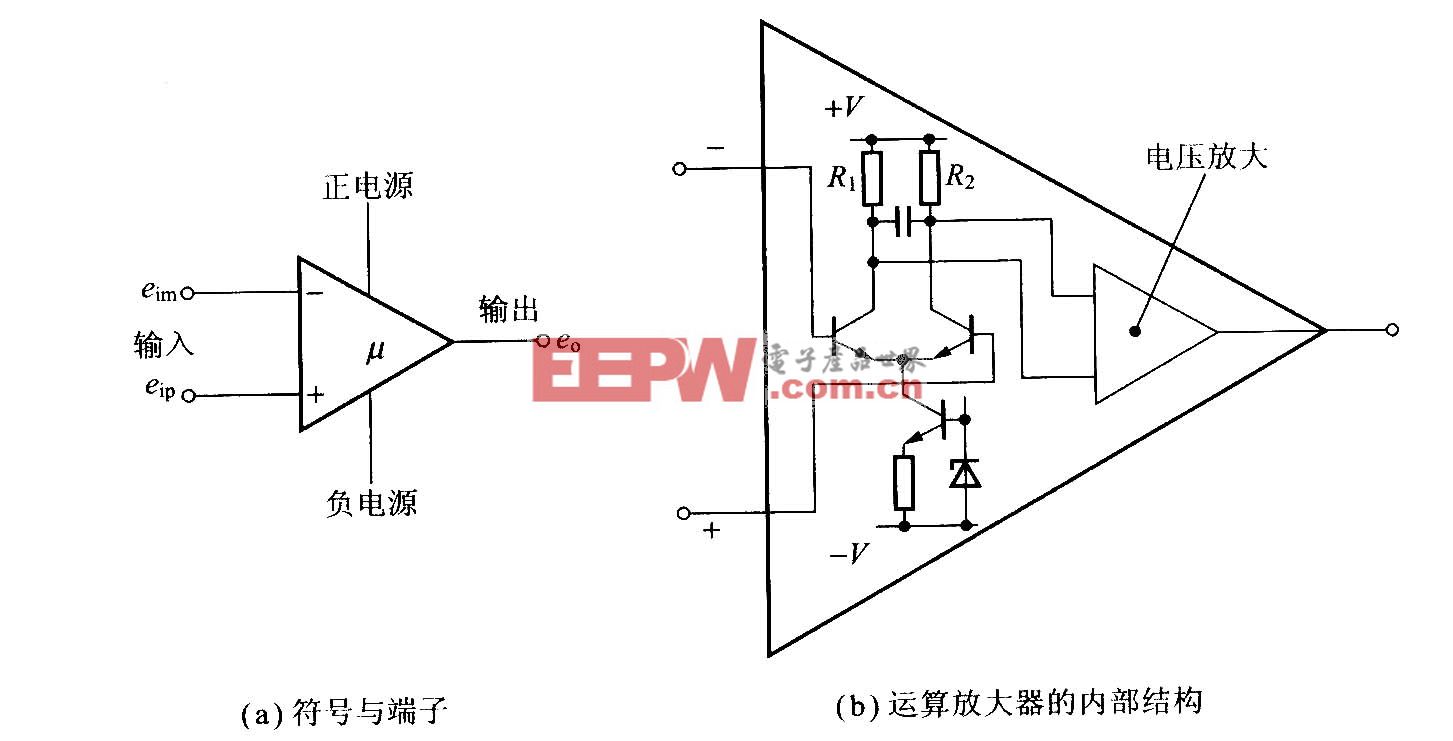

图1是该芯片待机功能的基本内部电路。管脚2外接两个电阻(RA和RB)和一个电容(CT),照图1中连接,是用来分别设置振荡器正常运行的工作频率(fosc)和待机模式的工作频率(fsb)。实际上,只要待机信号是高电平,该管脚能通过一个N沟道FET内部连于参考电压Vref,所以,定时电容CT通过RA和RB放电。当待机信号变低,N沟道FET就关闭且该管脚悬空,CT只通过RA放电,这样振荡器频率就会变低。VCT在正常运行中由Vref通过RA和RB控制,而在待机时通过RA来进行调控。当CT上的电压达到3V时,电容会快速地内部放电。当电压降到1V时,它开始再次充电。

图1 L5991芯片的待机功能基本电路

正常运行中RT将等于RA//RB,其频率公式为

fosc≌假如,由于负载减小使得主电流峰值降低,且Vcomp降低到一个固定极限(VT1)时,振荡器频率将被设置到一个较低的数值上(fsb)。假如,主电流峰值增加且Vcomp超过VT2时,振荡器频率将重置在正常值上(fosc)。频率的变化引起Vcomp的变化,并且由于能量平衡原因而方向相反,因而,提供一个恰当的滞后便可以防止振荡器频率在fsb与fosc之间变动。

3 反激式开关电源待机功能的实现

根据上述L5991芯片的待机原理,我们可以试想,在UC3842构成的反激式开关电源的基础上加入待机功能。通过对与负载相联系的反馈电压进行检测,利用芯片内部的误差放大器的输出值,对频率进行改变。

UC3842芯片的管脚1为误差放大器输出,图2为芯片待机功能的基本电路。

图2 芯片待机功能的基本电路

该电路的主要原理是:检测反馈电压经误差放大器后的输出值,通过一个迟滞比较器(施密特触发器),驱动开关管的开通或者关断,来实现RT的改变,从而改变电源的振荡频率。

我们可以看到,电源处于何种工作状态(正常工作或是待机),取决于迟滞比较器的阈值的设定,而该阈值取决于电源待机和正常工作时的误差放大器的输出值。

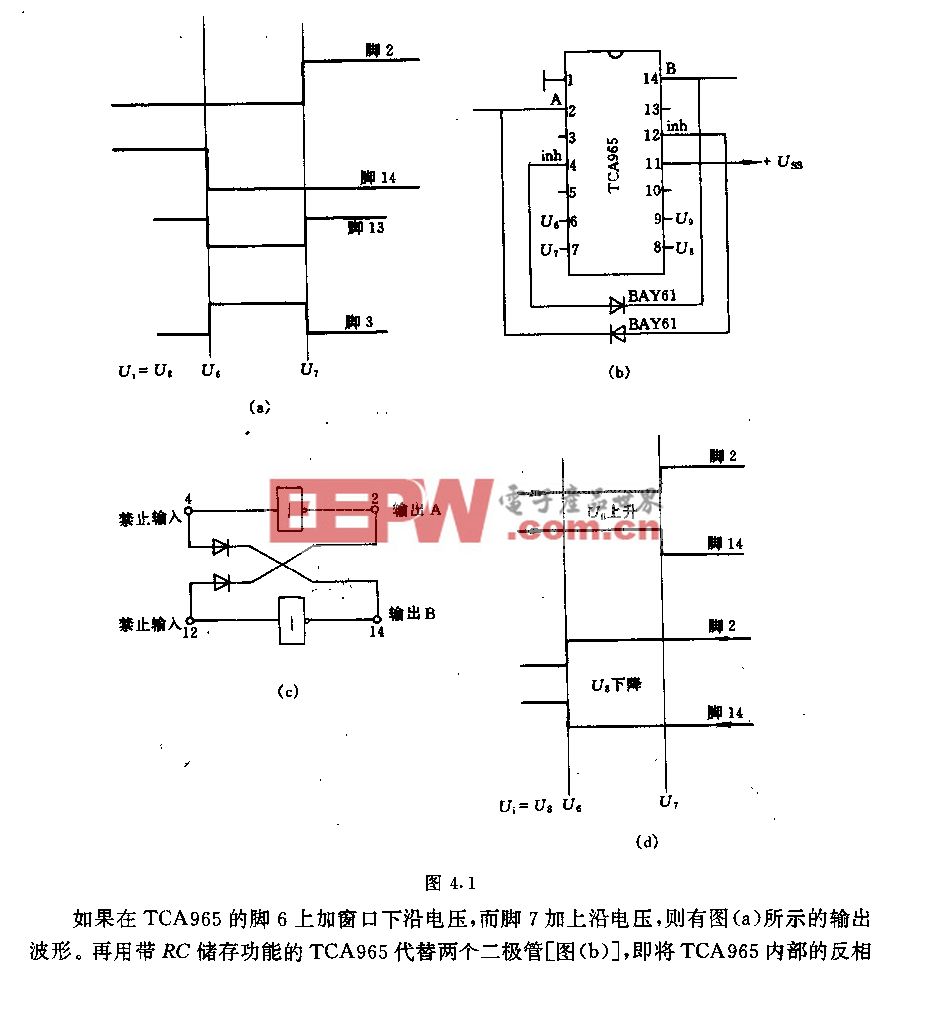

在实际设计的电路中,电源电路空载时,输出约为1.6V,而非轻载时为1.8V以上,因而,我们根据这个值来设定迟滞比较器的阈值。迟滞比较器由555芯片加上外围的电阻构成,该比较器的电路图如图3所示。

图3 迟滞比较器电路

图3中,555芯片的基准电源VDD为+5V,由UC3842的脚8输出基准电压给定。迟滞比较器的上下阈值计算如下:

VTH=VDD (3)

VTL= (4)

根据以上确定的阈值,确定各个电阻的阻值。

电源电路负载变化时,根据迟滞比较器的阈值,电源工作在相应的频率。

4 试验结果

根据以上原理搭构了由UC3842芯片控制的单端反激式开关电源电路[1][2][3],并加入了待机电路,其中取CT=4700μF,RA=RB=20kΩ,验证了以上原理。

5 结语

由UC3842构成的开关电源,完全可以加入待机功能电路来实现待机功能,在空载的时候降低开关频率,有效地减少开关损耗。并且,完全可以在其他PWM芯片上也加入类似的检测控制电路来实现待机功能。

pwm相关文章:pwm原理

评论