ML7204和PicoBlaze软核处理器实现低速话音编解码系统

ML7204专用语音处理器可提供多种速率的编解码功能,包括A律和U律2种不同的PCM和G.729A低速压缩话音编解码。该器件内置FIF0缓存器,具有合成语音质量高、抗误码性能好等特点,并在语音通信,特别是VoIP系统中应用广泛。基于8051构架的开源微处理器内核PicoBlaze配合FPGA解决常量编码可编程状态机(KCPSM)问题,可以使系统同时具备处理复杂控制和时序逻辑的能力。这里介绍了ML7204的基本性能和工作原理,微处理器内核PicoBlaze的开发流程及其使用方法,并且给出通过PicoBlaze配置、控制ML7204实现单路G.729A语音编解码的系统设计方案。

1 ML7204功能简介

ML7204具有如下特点:内置640字节FIF0,为数据收发提供缓存;支持ITU的G.711、G.729A等分组语音处理标准;回音抵消和抑制、静音检测和舒适噪音等提高分组语音处理性能;收、发增益控制;以数据、地址总线方式访问控制寄存器。

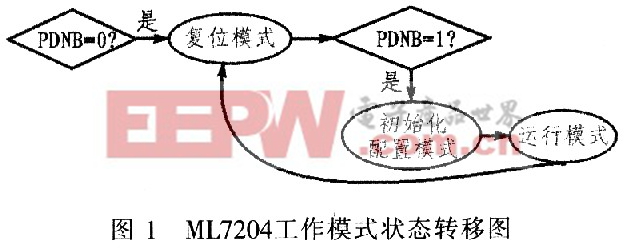

ML7204分组语音处理器件的接口是从硬件连接和功能两方面考虑,包括语音、PCM、中断、时钟、处理器等接口。其中,语音接口(Voice I/F)模拟话音信号的输入输出,内置可调增益放大器和A/D和D/A转换器;PCM接口(PCM I/F)用于非压缩语音信号的输入输出,为64 kb/s率或a率压扩的PCM信号;中断接口(INT I/F)提供异常状况的信号指示;时钟接口(CLK I/F)既可外置晶体,也可直接输入时钟信号,时钟频率12.288 MHz;处理器接口(MCU I/F)包括8位数据、地址总线以及读、写使能、片选信号,实现微处理器与ML7204的通信,并实现微处理器对ML7204的控制、以及ML7204的状态检测。ML7204有复位、初始化配置、运行3种工作模式,如图1所示。ML7204上电后,复位信号有效(PDNB=0)时,内核重启,则ML7204进入复位模式(Power Down State);初始化配置模式(Initial State)是当复位信号释放(PDNB=1)时,所有状态重置等待处理器配置。处理器通过修改控制寄存器完成器件的初始化配置;初始化完成后器件进入运行模式(OperationState),开始正常运行,此时通过设置PDNB或控制寄存器的软复位信号使ML7204重新进入复位模式等待初始化。

2 微处理器内核PicoBlaze简介

PicoBlaze的特点如下:Xilinx公司专为Virtex、Spartan系列FPGA和CoolRunner系列CPLD设计的嵌入式专用8位微处理器IP Core;占用逻辑资源少,只占96 slices(Sparta-3X(22S200E资源的5%):运行速度快,最高可达40 MI/s;指令集丰富,包括逻辑操作、输入,输出、算术运算等指令;开源、免费的编译器kcpsm3。

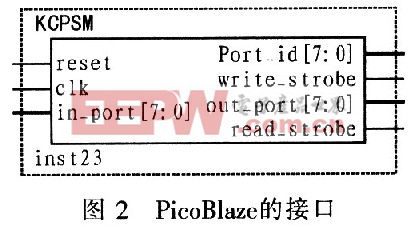

PicoBlaze微处理器接口从数据和控制两方面考虑,包括复位、时钟、读信号、写信号、数据输入、数据输出等接口。如图2所示。

复位接口(reset)是异步复位、高有效、清除PicoBlaze内核所有状态,但不清除程序代码;时钟接口(clk)是输入主时钟,最高速率35 MHz;地址总线接口(port_id[7:0])为PicoBlaze内核的地址总线,持续2个时钟节拍有效;数据总线接口(out_port[7:0])是PicoBlaze内核的数据总线,持续2个时钟节拍有效;读信号接口(read_strobe)是读脉冲信号,当该信号为高时,port_id[7:0]输出有效数据;写信号接口(write_strobe),写脉冲信号,当该信号为高时,port_id[7:O]输入有效数据。

评论