ML7204和PicoBlaze软核处理器实现低速话音编解码系统

3 系统硬件设计

图3为基于PicoBlaze软核处理器和ML7204编解码器的单路低速话音编解码系统的框图。本文引用地址:http://www.eepw.com.cn/article/157314.htm

该系统主要由话音信号处理、系统逻辑控制、传输复分接、时钟处理4个单元组成。其中,话音信号处理单元主要由ML7204和简单外围器件组成,完成模拟话音信号与G.729A压缩编码信号之间的相互转换;系统逻辑控制单元由PicoBlaze内核组成,完成与ML7204的数据传输;传输复分接单元由FPGA片内逻辑单元组成,完成拆、组帧及并、串转换。时钟处理单元为ML7204提供高稳定时钟信号。

由话机模拟电路输出的模拟话音信号经话音信号处理单元,实现PCM编码、G.729A压缩编码,再通过并行MCU I/F接口输出速率为8 kHz的G.729A压缩编码数据,系统逻辑控制单元读取压缩编码数据,并送往传输复分接单元,进行组帧、并串转换,最终输出成帧的串行码流。相应地成帧的串行码流先进入传输复分接单元进行帧同步检测,读取真正的话音数据,串并转换后,再传输至系统逻辑控制单元,由PicoBl-aze内核将并行话音数据发送至话音信号处理单元,话音数据经解压缩、PCM解码,恢复模拟话音信号。

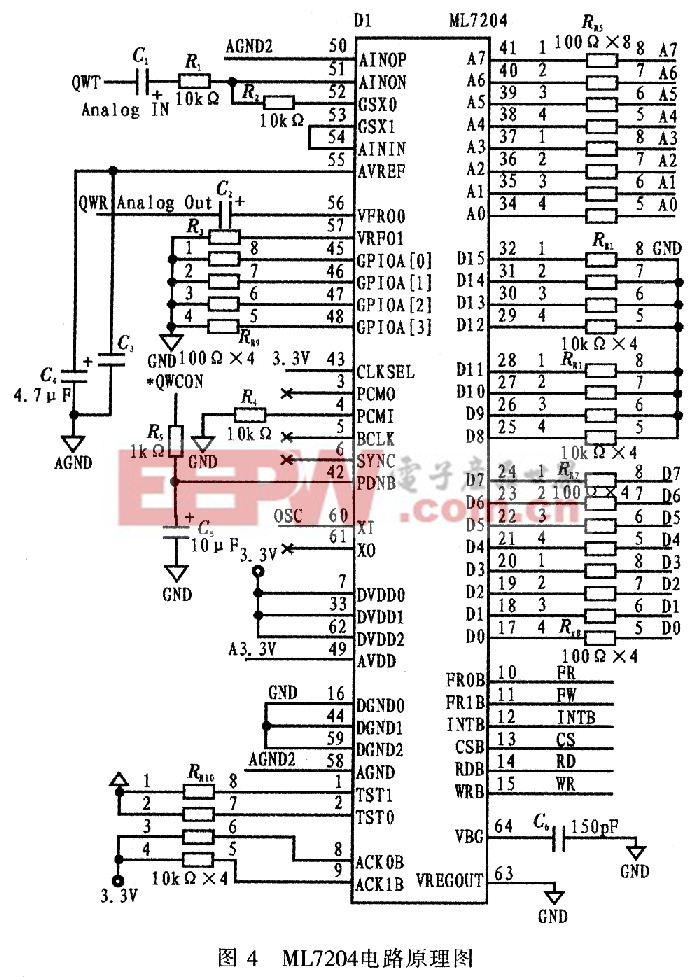

ML7204的数据传输采用总线方式,即A[7:0]、D[7:0]分别是8位数据、地址总线;FROB、FRlB、INTB、CSB、RDB、WRB分别为读使能、写使能、中断、片选、读信号、写信号。ML7204有10 ms帧和20 ms帧两种数据帧格式,这里采用10 ms帧格式。ML7204以10 ms为周期全双工并行工作。每隔10 ms,ML7204拉低读使能信号FROB,表示已经准备好完整的一帧数据,外部PicoBlaze微处理器通过连续10次拉低片选信号CSB、读信号RDB读出一帧数据。相应,每隔10 ms,ML7204拉低写使能信号FRlB,表示解码处理新的一帧数据,外部PicoBlaze微处理器可以通过连续10次拉低片选信号CSB、写信号WRB写入一帧数据。图4是ML7204电路原理图。

4 系统软件设计

该系统软件主要是对ML7204初始化配置、工作状态控制.ML7204的配置方式是修改控制寄存器。工作时,FPGA内嵌PicoBlaze内核首先对ML7204复位,复位成功后,PicoBlaze内核通过MCU I/F接口修改控制寄存器,设置其工作方式,包括语音编码方式、语音信号幅度、数据帧长度等,最后FPGA内部逻辑处理单元配合PicoBlaze内核完成分组语音数据的读写及传输。ML7204共有48个控制寄存器CR0~CR47,分别对应于地址00H~2FH,每个控制寄存器有8 bit数据,分别标识不同的配置选项。保留地址80H、81H分别对应分组话音编解码数据的读、写地址。图5为软件工作流程。

评论