标签

3D封装技术社区

3D封装技术社区

3D封装技术社区

3D封装技术社区

3D封装

- 3D封装资讯

- 3D封装专栏

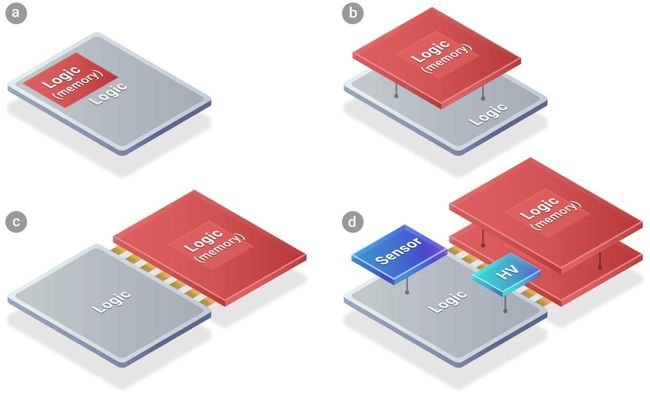

3D封装与TSV工艺技术

3D封装

2022-06-25

美国押注3D封装,为芯片未来做准备

3D封装

2022-04-14

- 3D封装资料

更多

最新帖子

相关标签