详细讲解Vivado设计套件带来的益处

多维度分析布局器

Feist 解释说,上一代FPGA 设计套件采用单维基于时序的布局布线引擎,通过模拟退火算法随机确定工具应在什么地方布置逻辑单元。使用这类工具时,用户先输入时序,模拟退火算法根据时序先从随机初始布局种子开始,然后在本地移动单元,“尽量”与时序要求吻合。Feist 说:“在当时这种方法是可行的,因为设计规模非常小,逻辑单元是造成延迟的主要原因。但今天随着设计的日趋复杂化和芯片工艺的进步,互联和设计拥塞一跃成为延迟的主因。采用模拟退火算法的布局布线引擎对低于100 万门的FPGA 来说是完全可以胜任的,但对超过这个水平的设计,引擎便不堪重负。不仅仅有拥塞的原因,随着设计的规模超过100万门,设计的结果也开始变得更加不可预测。”

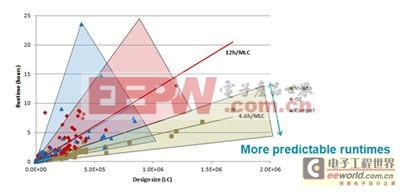

着眼于未来,赛灵思为Vivado 设计套件开发了新型多维分析布局引擎,其可与当代价值百万美元的ASIC布局布线工具中所采用的引擎相媲美。该新型引擎通过分析可以找到从根本上能够最小化设计三维(时序、拥塞和走线长度)的解决方案。Feist 表示:“Vivado设计套件的算法从全局进行优化,同时实现了最佳时序、拥塞和走线长度,它对整个设计进行通盘考虑,不像模拟退火算法只着眼于局部调整。这样该工具能够迅速、决定性地完成上千万门的布局布线,同时保持始终如一的高结果质量(见图1)。由于它能够同时处理三大要素,也意味着可以减少重复运行流程的次数。”

图1:与其它FPGA 工具相比,Vivado 设计套件能够以更快的速度、更优异的质量完成各种规模的设计

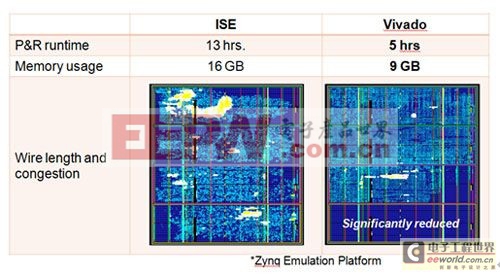

为展现这种优势,赛灵思在ISE设计套件和Vivado 设计套件中用按键式流程方式同时运行针对赛灵思Zynq-7000 EPP 仿真平台开发的原始RTL,同时将每种工具指向赛灵思世界最大容量的FPGA 器件——采用堆叠硅片互联技术的Virtex-7 2000T FPGA。这样Vivado 设计套件的布局布线引擎仅耗时5 个小时就完成了120 万逻辑单元的布局,而ISE 设计套件则耗时长达13 个小时(图2)。而且采用 Vivado 设计套件实现的设计拥塞明显降低(设计中显示为灰色和黄色的部分),器件占用面积较小,这说明总体走线长度缩短。Vivado 设计套件实现方案还体现出更出色的内存编译效率,仅用9GB就实现设计要求的内存,而ISE 设计套件则用了16GB。

Feist 表示:“从本质上来说,你看到的就是Vivado 设计套件在满足所有约束条件下,实现整个设计只需占用3/4 的器件资源。这意味着用户可以为自己的设计添加更多的逻辑功能和片上存储器,甚至可以采用更小型的器件。”

图2:Vivado 设计套件的多维分析算法可创建专门针对最佳时序、拥塞和走线长度(而不仅仅只是针对最佳时序)优化的布局。

功耗优化和分析

当今时代,功耗是FPGA设计中最关键的环节之一。因此,Vivado设计套件的重点就是专注于利用先进的功耗优化技术,为用户的设计提供更大的功耗降低优势。“我们在技术上采用了目前在ASIC工具套件中可以见到的先进的时钟门控制技术,通过该技术可以拥有设计逻辑分析的功能,同时消除不必要的翻转”Feist表示“具体来说,新的技术侧重于翻转因子‘alpha’,它能够降低30%的动态功耗”Feist说,赛灵思去年在ISE设计套件中开始应用该技术,并一直沿用至今。Vivado将继续加强这一技术的应用。

此外,有了这一新的可扩展的数据共享模型,用户可以在设计流程的每一个阶段得到功耗的估值,从而可以在问题发展的前期就能预先进行分析,从而能够在设计流程中,先行解决问题。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论