HBM竞赛白热化!SK海力士探索封装新方案 或满足英伟达峰值性能目标

《科创板日报》3月4日讯 据韩国ZDNet消息,SK海力士正在推进下一代封装技术,用于提高HBM4的稳定性和性能。目前该项技术正处于验证阶段。

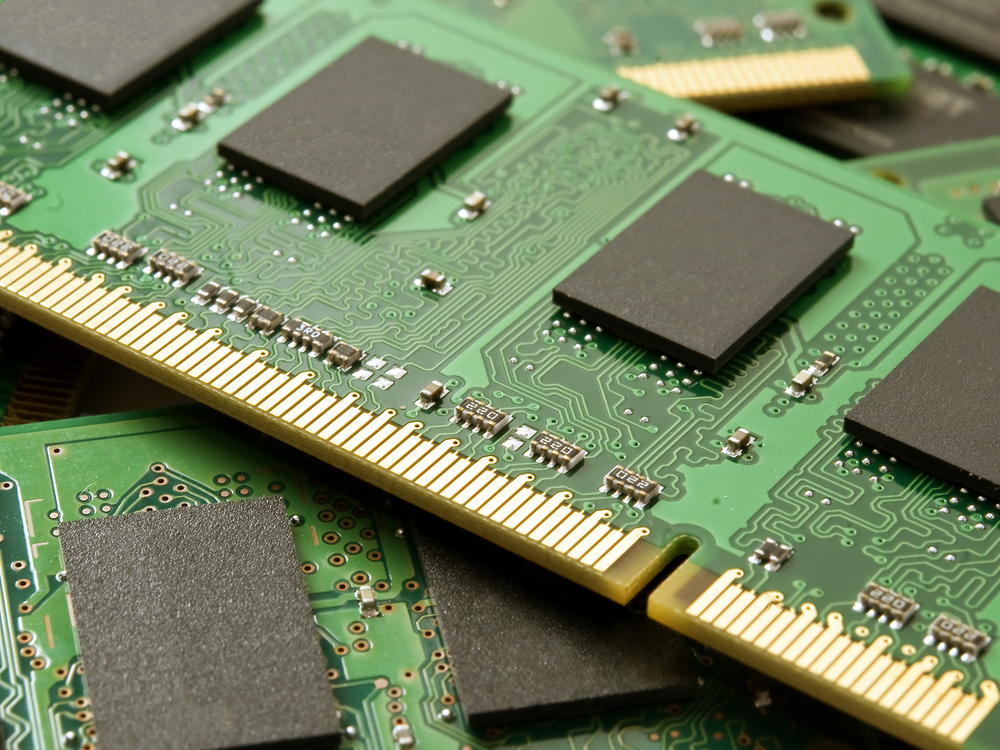

由于HBM4的I/O(输入/输出信号)数量翻倍至2048个,故而增加了信号干扰的风险。这种扩展虽然提升了带宽,但也带来了电压等方面的挑战。为增强稳定性,SK海力士计划增加部分上层DRAM芯片的厚度,同时缩小DRAM层之间的间距,以防止封装整体高度增加,同时降低向最上层供电所需的功耗,提高电源效率。

传统上,DRAM通过研磨背面来减薄芯片厚度,以满足HBM4 775微米的厚度要求。其风险在于,过度减薄会降低性能并增加对外部冲击的敏感性,这使得增加芯片厚度被SK海力士提上议程。

然而更窄的间隙使得向间隙中注入模塑底部填充材料(MUF)变得更加困难,为起保护和绝缘作用,封装过程中需均匀填充MUF以防止芯片缺陷。因此,SK海力士开发了一种新的封装技术,旨在不大幅改变现有工艺流程或设备的前提下,缩小DRAM间距并保持稳定的良率。

报道指出,近期其内部测试已取得积极成果,且若实现商业化,这项技术不仅有望达到英伟达要求的HBM4的峰值性能,还能显著提升下一代产品的性能。

此前有消息称,英伟达很有可能会降低其最初提供的 HBM4 的性能要求,使其达到10Gbps的水平。半导体分析公司Semianalysis表示,英伟达最初将Rubin芯片的总带宽目标设定为22 TB/s,但内存供应商似乎难以满足英伟达的要求,并且“预计初始出货量将低于此,接近20 TB/s(相当于每个HBM4引脚10 Gbps)。”

在此背景下,为追求更高市场份额,存储大厂间已然开启了HBM性能竞赛。如三星在采用更先进1c DRAM技术的基础上,于近期以来仍实施众多举措,包括但不限于增大DRAM芯片尺寸,引入全新供电架构(PDN分段技术)以降低HBM缺陷率等。

根据TrendForce集邦咨询最新报告,随着AI基础建设扩张,对应的GPU需求也不断成长,预期英伟达Rubin平台量产后,将带动HBM4需求。目前三大存储器原厂的HBM4验证程序已进展至尾声,预计将在2026年第二季陆续完成。

从各厂商进展来看,三星凭借最佳的产品稳定性,预期将率先通过验证,预计第二季完成后将开始逐季量产。SK海力士持续推进,且可望凭借与英伟达既有的HBM合作基础,在供应位元分配上保持优势。美光的验证节奏虽然相对较缓,也预计将会在第二季完成。

评论