1.2V I/O SPI NOR 闪存降低整体系统成本与功耗

如今,边缘人工智能、汽车、清洁能源和通信等新兴市场领域,广泛采用基于 10 纳米及以下制程的系统级芯片(SoC)。

先进 SoC 的工作电压低至 1.2V 甚至更低。若要支持许多 NOR 闪存采用的 1.8V 等高电压 I/O 结构,会增加 SoC 的芯片面积并提高成本。而具备 1.2V 输入 / 输出(VIO)特性的 NOR 闪存器件,既能降低成本,又能减少功耗。

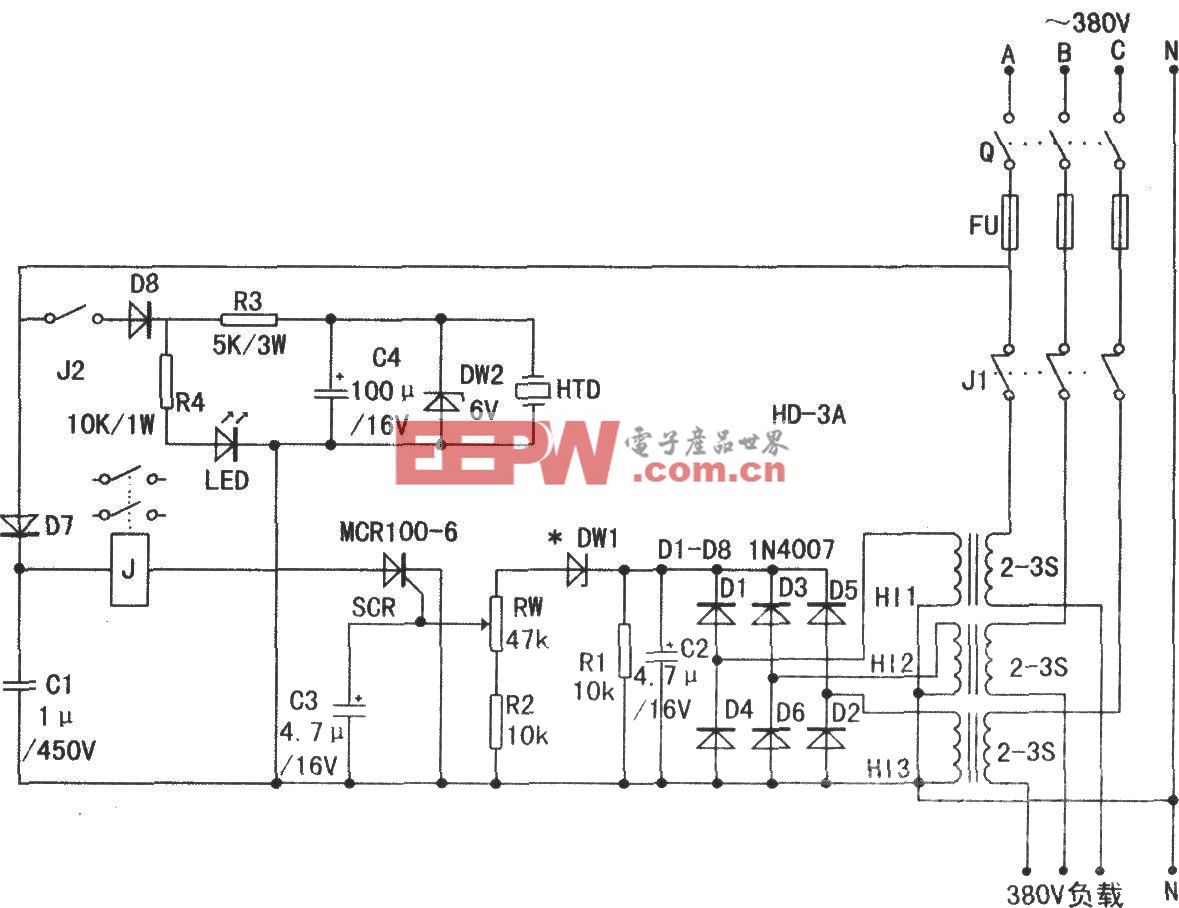

传统外部闪存器件的供电电压通常为 3.3V 或 1.8V,支持高速读取、快速编程和快速擦除等高性能操作。若将这些器件与 1.2V SoC 搭配使用,需额外配备电平转换器,或采用内置电平转换功能的 SoC。另一种方案是:闪存器件以 1.8V 为核心电压运行,同时通过 1.2V I/O 接口与 SoC 对接,由电源管理芯片(PMIC)提供两种电压(见图1)。

1. 1.2伏SoC与1.2伏VIO SPINOR闪存之间的接口不仅节省了功耗和电路板空间,还简化了I/O电压架构。

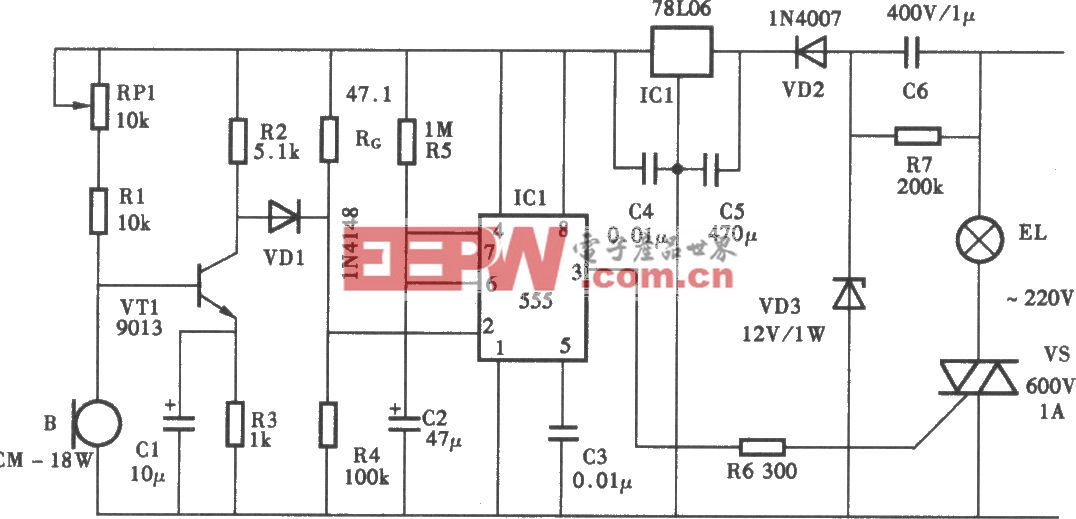

典型例子是向VCC和VCC_IO针脚供电为1.8伏和1.2伏(见图2)。CC_IO针是额外的引脚,作为I/O引脚的1.2伏电源电压。

2. 图中显示的是GigaDevice的GD25NE系列SOP16引脚,采用1.2伏VIO SPI闪存(左侧),BGA 5x5引脚,采用1.2伏VIO NOR SPI闪存设备(右侧)。

如今,有两种产品支持1.2伏SPI NOR闪存架构。一种是纯1.2伏SPI非诺闪存,支持1.2伏电源和输入输出;另一种则结合了1.8伏的磁芯电压和1.2伏的VIO接口电压。

纯1.2伏NOR闪存面临设计挑战,即实现1.8伏器件的全部性能。它在较低的1.2伏磁芯工作,该处内部闪存读取、编程和擦除作需要内在高于磁芯电压的内在高电荷电压。该方案支持低至中等性能应用,但可能无法应对需要双电压解决方案的其他高性能应用。

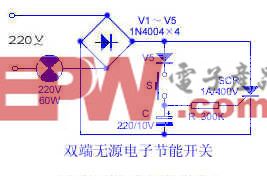

双电压VIO方案节省了大量电力(见图3)。

3. 传统1.8伏SPI诺尔闪存与1.8伏带1.2伏VIO SPI诺尔闪存的读写性能相似(左图),但双电压方案能实现50%的省电(右)。

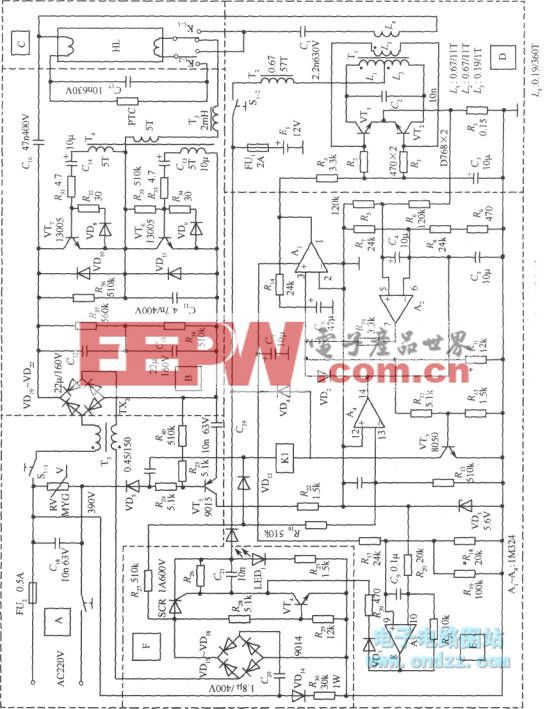

通过GigaDevice的GD25NE SPI NOR 闪存芯片的关机模式(见图4)可以降低整体功耗。在待机模式下电流降至12 μA,深度断电模式下降至200 nA。256字节页面程序时间为0.15毫秒,比传统的1.8伏SPI NOR闪存设备快约40%。

4. 不同工作模式下的功耗分布,包括读取、待机和深度断电,显示根据使用情况带来的额外节能效果。

评论