Arm的Cortex-R内核加强了对汽车级芯片控制

并非每个计算机系统都可以在引擎盖下切割它。

本文引用地址:https://www.eepw.com.cn/article/202503/468508.htm如今,数十个电子控制单元 (ECU) 可以分布在现代车辆周围。每个单元通常只需要足够的计算能力来完成从车身控制到动力总成等领域的单个任务。在许多情况下,这些计算机模块必须能够不间断地运行安全关键作。这意味着要利用紧凑、实时的汽车级微控制器 (MCU)。

Arm 的 Cortex-R 系列实时 CPU 内核采用与物联网设备到高端智能手机相同的节能架构,正在成为现代汽车的主要构建模块之一。

许多最大的 Arm Cortex-M MCU 供应商也提供各种基于实时 Cortex-R 内核的芯片,包括 Infineon、Microchip Technology、NXP Semiconductors、Renesas Electronics、Silicon Labs、STMicroelectronics 和 Texas Instruments。然而,近年来,这些公司一直在使用基于 Arm 的 Cortex-R5 及其对应产品 Cortex-R5F 的安全关键型 MCU 来提高他们的实时性能。

一些公司还提供芯片的多核变体,包括四核 Arm Cortex-R5F MCU。它们内部的实时 CPU 内核为引擎盖下的计算任务提供了足够高的性能,当然,还有在汽车应用中至关重要的实时行为。它的实时计算能力也是功能安全的一大优势。

Cortex-R5 基于 R4 的基本功能构建。它们包括增强的错误管理、扩展的功能安全和 SoC 集成功能,旨在为高度嵌入式实时和安全关键型汽车系统奠定良好的基础。

据 Arm 称,通过具有高度灵活的第二个内核来实现安全性,该内核可用于冗余或提高性能。Arm 表示,Cortex-R5 还从其更好的总线保护和纠错码 (ECC) 中脱颖而出。

Cortex-R5:Arm 实时 CPU 架构内部

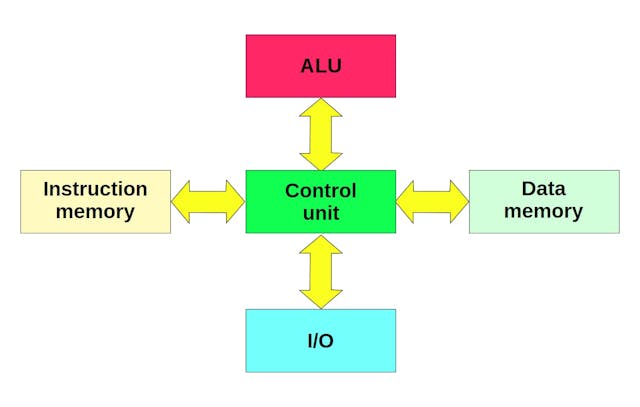

Cortex-R5 基于所谓的“哈佛”内存架构,这意味着它具有用于指令和数据的独立存储和信号路径(见图)。实时 CPU 内核增加了可选的集成指令和数据缓存控制器,同时其内部的缓存内存量非常灵活。这些缓存可以配置为 4 到 64 kB 之间,而回写和直写都是缓存行的选项。

CPU 内核核心的指令集是 Thumb-2。它将 32 位指令折叠到 16 位 Thumb 架构中,并支持数字信号处理。Cortex-R5 基于八级流水线微架构,具有指令预取、分支预测和选定的双发射执行。并行执行路径也是运行 MAC、shift-ALU、load-store、divide 和浮点 (FP)作的软件包的一部分。

Cortex-R5 最多包含一对紧密耦合的存储器 (TCM)。TCM 是直接连接到处理器内核的专用、低延迟片上内存区域,与标准外部 RAM 相比,可提供更快的访问速度,通常用于关键代码部分,例如中断处理程序和/或确定性时序至关重要的实时工作负载。A 和 B TCM 可用于代码和数据的任意组合,并且可以配置高达 8 MB。TCM B 还预置了两个物理端口,即 B0 和 B1。这提供了传入的直接内存访问 (DMA) 数据流的交错。

高度确定性或低延迟的工作负载可以在中断服务例程的指令代码和需要密集处理的数据等情况下利用可选的 TCM 接口,否则这些数据可能无法很好地响应缓存。

Cortex-R5 CPU 的其他可选构建块

Cortex-R5 包括一个可选的 MPU,可设置为使用 12 个或 16 个区域。反过来,这些区域(可以重叠)的分辨率低至 32 字节。编号最高的区域被授予最高优先级。

评论