高速数字电路封装电源完整性分析

去耦电容数量的影响

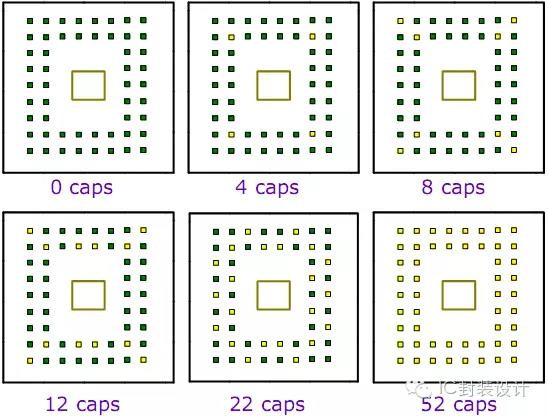

本文引用地址:https://www.eepw.com.cn/article/201610/311828.htm由前面的结果知道,电容放在封装上效果更好,所以对电容数量的探讨,以在Pkg上为主。在前述Pkg+PCB的结构上,Pkg上电容的放置方式如图9,模拟结果如图10。

图9 封装上电容的放置位置

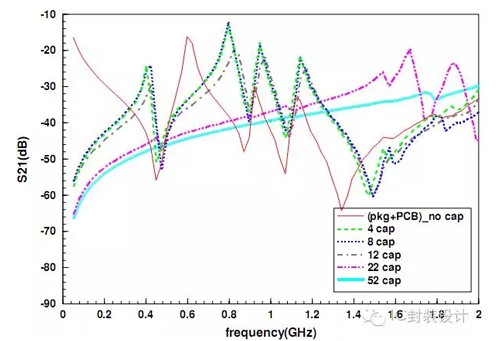

图10 电容数量对|S21|的影响

从测量结果可知,加4和8颗时,在0~200Mhz,能有效压低|S21|,但在400Mhz附近产生新的共振点,而把之后的共振点往高频移动。当加入12~52颗后,同样压低低频|S21|,且把400Mhz附近的共振点大大消减,高频共振点向高频移动,且振幅大为缩减。

随着电容数量增加,对噪声的抑制更好,从4~8颗的300Mhz,提升到1.2Ghz(52颗),所以增加电容数量,有助于对提高电源的噪声抑制能力。

去耦电容容值的影响

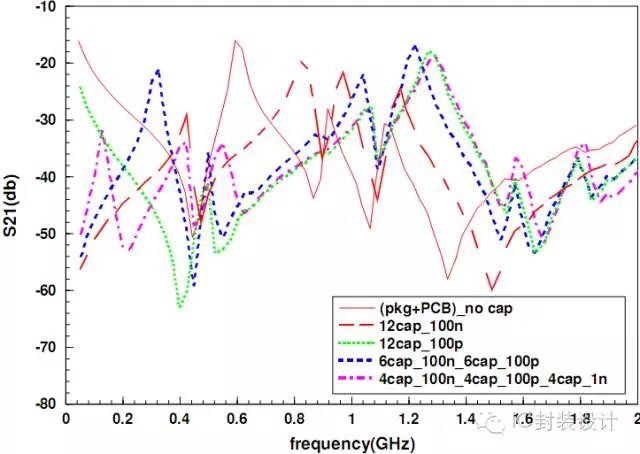

在Pkg和PCB的组合结构上,放置不同容值的电容,模拟结果如图11。

对加入100nF和100pF做比较,0~300Mhz间,100n大电容有较好的抑制效果;500~800Mhz,100p小电容有较好的效果;而加100n电容,会跟整个系统结构在400Mz产生共振;当使用100n+100p,200~600Mhz,比单纯使用100n和100p差,而更低频或更高频也没有单一容值好;当使用100n+1n+100p三种容值时,产生了更多共振点,在电子系统中要特别小心,如果电路产生的噪声刚好在共振频率点,则噪声被放大,对信号产生影响或辐射。

所以对电容容值的选择,应根据要抑制的频段来决定,频段决定后根据电容的共振点选择电容,越低的电容ESL和ESR越好。

图11 混合不同容值电容的模拟结果

板层厚度的影响

首先,固定PCB电源与地平面之间的距离为0.7mm,改变Pkg电源层厚度依次为1.6mm、0.8mm、0.4mm、0.15mm,结果如图12所示;当Pkg电源层厚度越来越高,第一个零点向低频移动;从前面结论知道,2Ghz前的噪声来自PCB,从结果来看PCB耦合上来的噪声也变大了,而2Ghz以后主要受封装影响,可以看到|S21|也随厚度而变大,所以Pkg电源平面的厚度对S参数影响是很大的。

图12 不同Pkg电源层厚度对|S21|的影响

评论