芯片设计中的功耗估计与优化技术

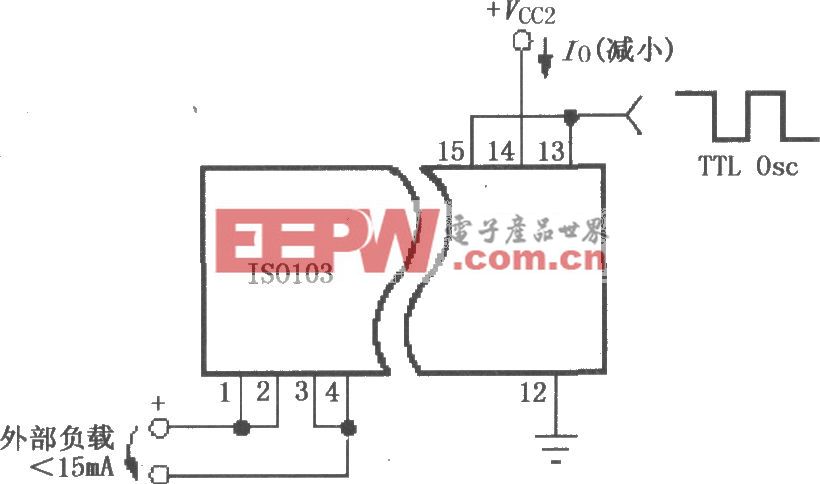

(图8)

本文引用地址:https://www.eepw.com.cn/article/201609/303352.htm通过set_clock_gating_style的下列选择,设计者可以控制门控单元的选取,如图9所示。

图9

选择考虑:

1)latch:用还是不用,是个问题。

latch-free的方案中,EN信号必须在时钟负沿前稳定,否则时钟会出现毛刺, 造成只留给EN产生逻辑半个时钟周期的时间。latch-based方案则不存在这个限制,但引入latch使时序分析,测试复杂性增加。故选择哪种方案需要设计者权衡决定。

2)正沿/负沿寄存器需要指定不同的门控单元

比如latch-based方案:正沿FF用and门,负沿FF用or门

3)integrated clock-gating cell/普通单元

在生成库的过程中,可以创建专门的集成时钟门控单元,以获得较好的时序。

4.4.3 时序分析

通过set_clock_gating_style -setup -hold 或 set_clock_gating_check指定。

AND门(图10)

图10

OR 门(图11)

图11

数值需要考虑到时钟歪斜的影响。

4.4.4 与dft流程的配合

1) 加入控制点(图12)

控制点的位置和控制信号可通过下面指令控制:

dc_shell> set_clock_gating_style -control_point before -control_signal scan_enable

图12

2) 加入观察点(图13)

在测试中,EN信号和control logic中的信号是测不到的,解决方式是加入观测逻辑。

dc_shell> set_clock_gating_style -control_signal test_mode

-observation_point true

-observation_logic_depth depth_value

图13

在测试模式,观察逻辑允许观测ENL信号,在正常操作模式,XOR树不消耗能量。

3) 测试信号与顶层测试端口连接

时钟门控单元的测试信号需要和顶层的测试端口相连,通过下指令进行,如图14所示。

图14

如果顶层有指定端口,将直接相连,否则,会创建此端口,并连接。

4.4.5 结果

在插入时钟树后,可以用report_clock_tree_power来获得时钟网络的功耗信息。

时钟门控经设计实践证明是一个行之有效的降低功耗手段,下图是基于一项真实设计的评估:(见参考文献[6])

图15

5 结语

在现代芯片设计中,功耗越来越引起设计者的关注。在本文中,我们首先分析了功耗的组成部分,然后阐述了功耗估算的方法,通过功耗估算可以使设计者在设计初期及时评估设计方案的效率,以便做出最优的选择。最后,重点分析了功耗优化的手段,包括架构优化,RAM功耗降低,时钟门控三种技术,并对引进时钟门控技术时若干难点逐一提出了解决方案,如门控单元选择,时序分析,测试支持等。功耗分析与优化二者相辅相成,设计者善加使用,方可事半功倍。

评论