英特尔14nm制程比台积电强太多 但龙头优势难保

过去几年时间里,英特尔虽然在桌面领域仍过着“无敌是多么空虚”的日子,但是围绕其芯片制造技术的话题讨论越来越多了,特别是与很多开始被人熟知的芯片制造厂商相比,比如台湾的芯片制造商台积电。

本文引用地址:https://www.eepw.com.cn/article/201603/287770.htm很多话题讨论的开始,均是基于每一次非英特尔芯片制造商对制造工艺的升级。最初,台积电和三星明确表示,将以最快的速度从“20 纳米”过渡的“14/16纳米”,而且将会重点发展称之为“FinFET”的晶体管结构器件,重点宣传新工艺相比传统而言芯片面积将得到大幅缩减,适配每一代工艺制程。

另一方面,当时英特尔也正处于 22 纳米工艺技术到 14 纳米的过渡中,并且英特尔也掌握了第二代 FinFET(Tri-Gate)器件技术。不过,英特尔的动作太慢了,导致三星和台积电各自挑衅称,其 16 和 14 纳米已经领先英特尔,而英特尔仍无法完全脱离 22 纳米的工艺制程,并且还有事实证明,台积电的 20 纳米工艺的晶体管密度比英特尔的 22 纳米更高。

英特尔从 22 纳米过渡到 14 纳米的时间实在过于漫长,这点不假,而且英特尔也意识到了,在工艺制程技术同步发展的过程中,晶体管密度的竞争相当重要。事实上,面对民间乃至业界广为谈论的误导性话题,英特尔并没有刻意的做任何回应,但当英特尔正式公布自家 14 纳米技术时,才真正确定了不可动摇的领先地位。

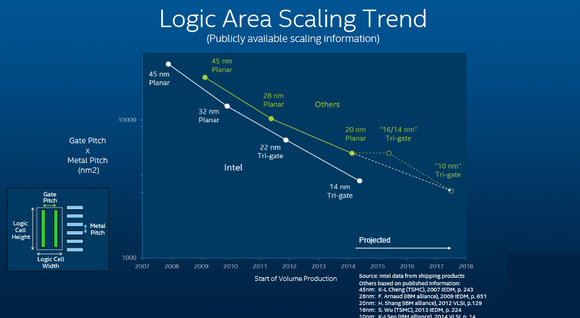

下图为英特尔官方提供的逻辑面积比例图:

从这个英特尔的图来看,英特尔承认自家的 32 纳米不如 28 纳米工艺,主要是指栅极与栅极之间的间距前者不如后者。再到 22 纳米与 20 纳米工艺的对比,结果亦是如此。不过,确实只有在 14 纳米和 16 纳米工艺节点,才超过了其余竞争对手,确立起领先的地位。

所以,三星和台积电所说的都是事实,这两大越来越出色的芯片代工厂在 20 纳米制程时代确实领先于英特尔 22 纳米。但不可否认英特尔新一代 14 纳米更为出色,至少晶体管密度的优势上超过了其他对手的 14/16 纳米工艺节点。

工艺是一回事,那晶体管的实际性能呢?

多年以来,英特尔从未放弃过任何吹嘘自己的芯片技术,只是在台积电和三星上位之后收敛了很多。而且,难能可贵的是英特尔竟然没有过度宣传自家的第二代 FinFET 工艺,毕竟其余竞争对手在其 14 纳米问世时,均处于第一代 FinFET 工艺水平。简单的说,英特尔 14 纳米正式问世之初,从晶体管性能的角度来看,整整领先了竞争对手一代。

在很多对芯片深度评测的机构报告中,尤其是权威站点 ChipWorks,我们可以看到英特尔 14 纳米晶体管所有性能指标均领先于其他竞争对手。更重要的是,ChipWorks 通过先进的透射电子显微镜观察分析发现,英特尔 14 纳米芯片的晶体管鳍片间距做得最为紧密,堪称这个星球上迄今最先进的半导体工艺,全面领先代工厂的 14/16 纳米。

评论