如何实现FPGA到DDR3 SDRAM存储器的连接

延时锁定环路(DLL)在整个PVT范围内将相位保持在一个固定位置。DLL模块的相位比较器用于将两个输入之间的相位差保持在零。实现的方法是均匀地修正DLL模块中的特定延时(10-16)。用于更新DLL中某个延时模块的控制信号还被发送到DQS输入路径中的时延模块。例如,可以利用DLL中的全部16个延时单元和DQS相移输入路径中的第4个延时抽头来实现90°的相移:

或者选择DLL中的10个延时单元和DQS相移输入路径中的抽头4来实现36°的相移:

或120°:

该DLL采用频率基准为每个DQS引脚中的延时链动态产生控制信号,并允许它补偿PVT的变化。在Stratix III FPGA中有4个DLL,它们都位于器件的边角,目的是使每个DLL能够覆盖器件的两侧,从而可以在器件的各个边上支持多种DDR3 SDRAM存储器接口。

跨越高速数据率域和设计简化

DDR捕获寄存器和HDR寄存器支持数据从双倍数据率域(数据在时钟的两个边沿)安全传送到SDR域(数据位于频率相同的时钟的上升沿,但数据宽度加倍),再到HDR域(数据位于时钟的上升沿,数据宽度仍是加倍,但时钟频率仅是SDR域的一半),这样使得内部设计时序更容易实现。

裸片、封装和数字信号完整性改进

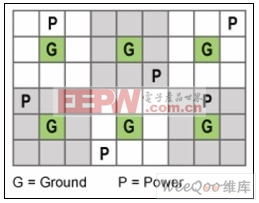

FPGA裸片和封装的设计必须为高性能的存储器接口提供更好的信号完整性(即用户I/O与地和电源的比例为8:1:1,并具有最佳的信号返回路径,如图3所示)。此外,FPGA应该提供动态OCT和可变的偏移率,以便能够控制信号的上升和下降时间以及可编程驱动能力,从而满足所用标准(即SSTL 1.5 Class II)的要求。

图3:连接到每个电源和地的8个用户I/O。

本文小结

高性能Stratix III FPGA可以通过提供高存储器带宽、改进的时序余量以及系统设计中的灵活性来弥补高性能DDR3 SDRAM DIMM的不足。由于DDR3在实际使用中将很快超过DDR2,故提供更低成本、更高性能、更高密度和优异的信号完整性的高端FPGA必须提供与JEDEC兼容的读写均衡功能,以便与高性能的DDR3 SDRAM DIMM相接。FPGA与DDR3 SDRAM的有机整合将能够满足目前和下一代通信、网络以及数字信号处理系统的要求。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论