处理器核未来像逻辑门一样常用和常见

摘要:多核的新架构——网状架构,可使核数增加时,性能呈线性增长,是多核领域提高芯片整体性能的一种有效方法。本文介绍了Tilera公司的Tile 64及发展思路。

本文引用地址:https://www.eepw.com.cn/article/89851.htm关键词: 多核;网状;总线;64核

当前,提高芯片处理能力通常采用两种方法:一种是把每个核的性能提高;另一种是在一个芯片里大力增加核的数量。Intel主要通过提高核的性能,因此主频做得很高,但功耗牺牲也较大。Tilera的技术路线是通过在一个芯片中设置多个核数来实现,同时把每个核做得很有效。

新兴的多核处理器供应商美国Tilera公司看好多核架构的发展前景,声称未来处理器核就像逻辑门一样成为基本的常用单位。根据摩尔定律推论(表1):2014年,将有1000个核的处理器出现。

表1 根据摩尔定律推论的多核的未来,每18个月核的数量将翻番

多核架构首先应用于高端计算市场,例如网络、数字多媒体和无线网等方面,例如网络速度正在向从1Gbps向10Gbps发展,多媒体领域的高清H.264编码、VoD、视频会议等需要高性能和多种服务等。

但是多核也有其发展瓶颈:当核数增加时,性能往往不能相应增加。这阻碍了芯片中核数的增长。Tilera公司摒弃了以前的总线架构,而开拓性地采用了网状(mesh)架构。

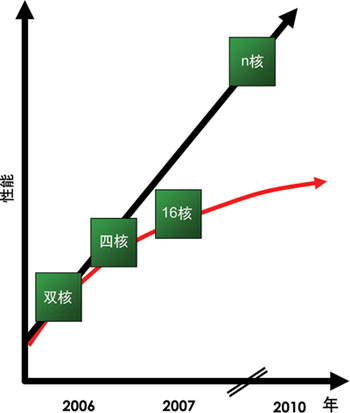

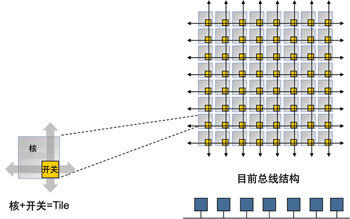

“Tilera的Tile64的功耗只有Xeon的1/30。” Tilera公司CTO(首席执行官)Anant Agarwal语出惊人,他解释说,因为固有的多核架构存在一些发展瓶颈,例如性能难以扩展,功耗也较高,编程复杂,因此随着处理器核数的增高,处理器的总体性能会打折扣(图1)。而Tilera的多核方案填补了核数与性能之间的鸿沟,其架构是核呈网状网络连接,而非传统的总线型。网状的特点是每个核上都有一个开关(switch),因此网状可扩展,大大地提高了核间互联效率,从而大大降低了功耗,节省了散热成本,而且模块易于布局和验证(图2)。

图1 总线架构:核数增多时,形成性能曲线

网状架构采用“核+开关”方式,性能可随着核数的增长而线性增加。

图2 网状和总线型示意图

Tile64处理器采用90nm的制程工艺,具有64核,片上分布cache有5MB,片上互联带宽达到32 Tbps;功耗方面,在进行H.264编码时,功耗只有8W左右;I/O带宽达40Gbps;除了性能提高外,Tile64还容易软件编程,采用通常的编程语言即可,例如ANSI标准的C/C++,SMP Linux语言等,并解决了多核任务分配的难题。2008年9月底,该公司又推出了增强版Tile Pro 64和32核产品,性能比原产品性能增强2.5倍。

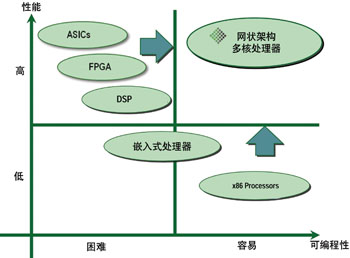

图3 Tilera的性能示意

“根据我们的性能比较,Tile64相当于10个双核Xeon处理器,或者20个DM648 DSP。”Tilera亚太区董事总经理吴晓东说:“Tilera的产品集通用处理、信号处理和FPGA的性能于一身,比传统方案大大提高了集成度。例如在网络和视频应用上,相较于DSP方案,由于节省了多个DSP芯片的占位面积,因此板卡较小。而FPGA的应用瓶颈是不能用通用编程语言,需要专门学习编程方法,如VHDL和Verilog语言。”

当核数较少时通常采用总线结构,核多时网状具有优势。Tilera公司可谓网状架构的先锋。公司2004年10月公司成立,2007年8月推出第一款芯片。虽然成立只有4年时间,但是Tilera的CTO Anant Agarwal同时也在MIT(麻省理工学院)CSAIL(计算机科学人工智能实验室)工作,他所在的CSAIL 1994年就开始了多核研究,Tile多核技术是在美国国防和国家科学委员会倡导下研发,并全权授权给Tilera公司进行商业推广。Tile64是基于第二代的Tile技术,并且已经实现了量产。

参考文献:

1, 多核时代,嵌入式编程和应用之出路,电子产品世界,2007.8

2,迎九,双剑合璧,营造网络设备多核应用新契机,电子产品世界,2007.7

3,韩青,多核调试新方法探讨,电子产品世界,2007.12

4,包益平、沈海、彭翔宇,英特尔推动多核技术在嵌入式系统的应用,电子产品世界,2008.6

5,Kevin Krewell、梁合庆,翘首以待多核伸缩软件的首次细节披露――微软FPF05语言探讨方案要点,电子产品世界,2006,2

评论