基于ADSP-BF533和EPM7160实现的多路UART接口电路设计

0 引言

本文引用地址:https://www.eepw.com.cn/article/85223.htm目前,在数字信号处理技术中,DSP+CPLD是控制接口设计中比较常用的方式。然而,AD-SP-BF533虽有异步串口,但该芯片只有一个异步串口,当一个系统中出现多个UART接口时,ADSP-BF533就显得无能为力了。为此,本文采用CPLD来实现多路UART接口的设计,以满足ADSP-BF533与多路UART接口的通信。

1 ADSP-BF533简介

ADSP-BF533处理器是Blackfin系列产品中的一员。其最大工作频率可达600 MHz。Blackfin处理器内核包含有2个16位乘法器、2个40位累加器、2个40位ALU、4个视频ALU和1个40位移位器,可处理来自寄存器组的8位、16位或32位数据。

该处理器包含有丰富的外设,可通过不同的高速宽带总线与内核相连。该系统不但配置灵活,而且有极好的性能。通用外设包括UART、带有PWM(脉冲宽度调制)和脉冲测量能力的定时器、通用I/O标志引脚、实时时钟和看门狗定时器等。

该处理器有多个独立的DMA控制器,能够以最小的处理器内核开销自动完成数据传输。DMA传输可以发生在ADSP-BF533处理器的内部存储器和任一有DMA能力的外设之间。此外,DMA传输也可以在任一有DMA能力的外设和已连接到外部存储器接口的外部设备之间完成(包括SDRAM控制器、异步存储器控制器)。有DMA传输能力的外设包括SPORTs、SPI端口、UART和PPI端口。每个独立的、有DMA能力的外设至少应有一个专用DMA通道。

ADSP-BF533处理器有16个双向通用可编程I/O引脚(PF15-0)。每一个可编程引脚对标志控制寄存器、标志状态寄存器和标志中断寄存器的编程均可独立控制。标志方向控制寄存器可规定每个独立的PFx引脚的方向,并可用作输入或输出。

ADSP-BF533该处理器提供有1个全双工的通用异步接收/发送(UART)端口,并与PC标准的UART完全兼容。UART端口可为其它外设或主机提供一个简化的UART接口,并可支持全双工、有DMA能力的异步串行数据传输。UART端口可支持5~8个数据位、1或2个停止位以及无校验、奇校验、偶校验位。UART端口的波特率、串行数据格式、错误代码的产生和状态、中断等均可编程设置。

2 ModelSim仿真工具

ModelSim为HDL仿真工具,利用该软件可对所设计的VHDL或Verilog程序进行仿真。Model-Sim支持IEEE常见的各种硬件描述语言标准。

Modelsim仿真工具是Model公司开发的。它可以支持Verilog、VHDL以及它们的混合仿真,也可以将整个程序分步执行,使设计者直接看到自己程序的下一步要执行的语句,而且在程序执行的任何步骤、任何时刻,都可以查看任意变量的当前值,也可以在Dataflow窗口查看某一单元或模块输入输出的连续变化等情况,因而比quar-tus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

3异步串口原理

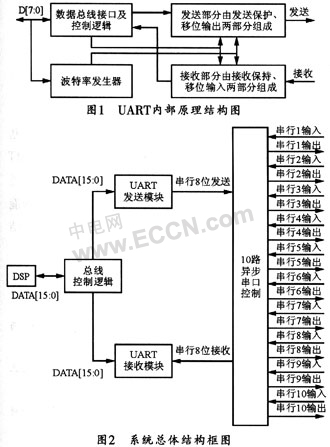

UART(Universal Asynchronous Receiver/Trans-mitter)通用异步收发器是用于控制计算机与串行设备的芯片。它提供有RS-232C数据终端设备接口,因此,可以通过计算机和调制解调器或其它使用RS-232C接口的串行设备进行通信。UART内部结构原理如图1所示。图2所示是其系统总体结构框图。图2中的总线控制逻辑主要用于完成数据总线的方向控制。

UART发送模块中16位并行数据的高4位用来控制是发向第几路的数据,低八位则是要发给该路异步串口的数据。发送模块中还有一部分用来把并行低8位数据转化成串行8位数据,然后再根据并行数据的高4位判断发往哪一个异步串口。

UART接收模块中,把接收到的8位串行数据转化成并行数据送到总线控制逻辑,然后通过中断通知DSP来读取。

这样就实现了通过DSP的并行数据总线来控制10路异步串口的收发数据。

4波形仿真

4.1发送模块的仿真波形

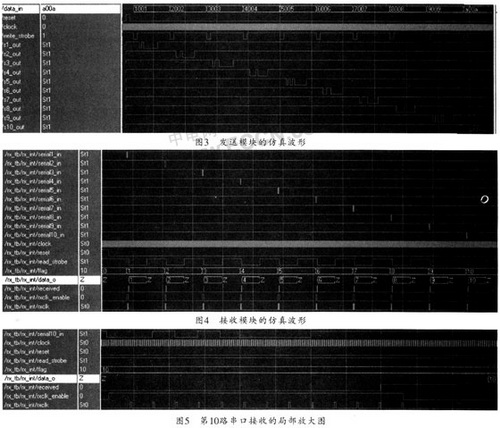

本设计中的EPM7128采用24.576 MHz的晶振输入,使用时应根据外部的串口波特率在内部通过编程对此输入时钟进行相应的分频处理。其发送模块的仿真波形图如图3所示。图中,data_in是DSP输入的并行16位数据,reset可用来复位,高电平有效;write_strobe是DSP的写信号;sl_out~s10_out分别是异步串口1~10的输出。为了验证本设计的灵活性,可以控制不同的串口让其输出不同的数据,也就是由串口1~10分别输出1~10的数据。

在发送模块中,通过检测write_strobe的下降沿可以把并行数据存储到CPLD中,再使能发送时钟,并给数据加上起始位0、校验位、停止位1,然后按照发送时钟的节拍把数据一位一位的发送出去。

4.2接收模块的仿真波形

在EPM7128中编程检测输入串口数据的下降沿,并使能接收时钟,然后即可开始接收数据。接收数据时,要把接到的第一位数据去掉,然后取第2~9位数据,这样就把起始位去掉了,从而得到八位数据。接收模块的仿真波形如图4所示。

seriall_in~serial10_in是第一路到第十路串口的接收端口,它们的输入数据依次是1~10;clock是系统时钟;reset是系统复位,高电平有效;read_strobe是DSP的读信号;flag是通道选择,用1~10分别对应开通第1路到第10路串口通道,图5是第10路串口所接收的信号局部波形放大图;data_0是并行数据输出;received8位串行数据接收完毕后,通过高电平向DSP发出的中断请求信号,以便DSP通过读信号read_strobe读取数据;rxclk_enable是接收串行数据时钟使能;rxclk是接收串行数据时钟。

从图5的放大图可以看出,在串口没有接收数据时,data_o为高阻状态,txclk_enable是低电平,因而不使能,txclk没有接收时钟,received是低电平,没有置高;而当开始接收数据时,data_o是高阻态,txclk_enable为高电平使能,tx-clk有接收时钟;此后再当接收完数据时,re-ceived为高电平并向DSP发送中断请求信号;此时,DSP响应中断,并通过read_strobe置低来读取数据,从而使数据10出现在并行数据线上。

现在可以从serial10_in结合rxclk来分析接收到的数据,串行数据依次是0010100001,因为第一位0是起始位.故数据从第二位算起的八位数据是01010000,又因数据是低位先发,因此,真正的数据是00001010(十进制数是10),由图中可以看到,data_o上输出的确实是10。

5 结束语

当一个系统中存在多个异步串行接口时,基于ADSP-BF533和CPLD设计的、具有多路UART接口的系统,可以方便的分别与多个异步串口进行通信,而且灵活性比较强,成本也很低,功能也比较完善。目前,该设计经实际板子验证,结果证明完全可行。

评论