自由IP Core资源的利用

摘 要:本文介绍了与免费IP Core运作有关的问题以及免费资源的若干来源,然后通过对两个不同来源的、免费的八位RISC CPU进行比较和分析,给出了若干选用免费核时应考虑的问题。

关键词:IP Core; CPU

引言

随着集成电路单位面积晶体管数量的激增和人们对缩短设计周期的追求,设计重用已经成为有效的应对方法,它不但适合于ASIC,也适合于CPLD/FPGA。在CPLD/FPGA的设计过程中,由于开发工具的通用性、设计语言的标准化,设计过程几乎与所用器件的硬件结构无关,设计成功的逻辑功能块也具有很好的兼容性和可移植性,从而使得产品设计效率大幅度提高。这些具有可再利用功能的逻辑功能模块都可以成为IP Core,因此IP Core可以是算法核、加密核、微处理器等。TI公司认为,一个ASIC设计80%的功能可用IP Core等现成逻辑合成,未来大系统的CPLD/FPGA设计将仅仅是各类再应用逻辑与IP Core的拼装。

自由IP Core

为何免费

目前有许多商业公司出售IP Core ,但价格昂贵,原因之一是高昂的开发费用。据测算,在IP Core的整个过程中,编写源代码所花费的成本只占总成本的10%,而调试和修正则占50%,市场销售和支持占到40%。如果将整个成本分摊到多个主体,那么对于单个主体而言成本就大大降低了,这就是设计开放共享的IP Core的初衷。由组织开放IP的机构将自愿参加者的设计开放,使用者可以找到设计的错误,或加入新的内容对原设计加以完善,使IP Core趋于成熟。同时CPLD/FPGA的生产商公布芯片的编程技术或者提供免费的EDA设计工具,从而使开放式硬件的设计者可以将该公司的芯片应用于新设计的系统,由此达到“多赢”的目标。

充分意义上的硬件开放必须达到三个条件:首先,硬件的接口必须清楚地公布出来,这样才能由他人自由的使用;其次,硬件设计本身必须公布于众,这样他人才能将其在不同的应用中加以实现或纠错;最后,应尽量采用免费的设计工具,以便于其他使用者对设计进行改进。

知识产权归属和法律问题

免费IP Core常用的认证有GPL、LGPL等。这两种认证原来是用于自由软件的,现已推广到对自由 IP Core的认证。大多数的软件认证都不允许对软件共享与修改,而GPL认证则旨在保证共享与修改软件的自由,确保软件对于所有的用户都是共享的。GPL认证为了确保用户有传播自由软件副本、根据自己的需要进行修改的自由,规定在传播软件的副本时,必须给予接受者同样的权利。必须确定他们收到或者可以得到源代码,并且知道这些条款,即自己的权利。

LGPL认证应用于某些特别指定的软件包——共享库。这一许可允许将这些库连入某些非共享程序中。在法律上,当程序中连入某个库,不论是静态的还是使用共享的库,这两者的结合都是原始库的派生,因此,只有整个结合物符合共享的标准,GPL认证才允许这种链接。但LGPL认证则以更宽松的准则允许其它代码和库的连接,因此在与非共享软件的竞争中,与GPL认证相比,LGPL为共享软件开发者提供的利益少一些。正是由于这一原因,许多库使用GPL认证,然而,在某些特殊情况下LGPL认证是有利的。例如:在特殊的情况下,可能需要鼓励某种库的广泛使用,以使其成为事实上的标准。为了达到这一目的,就会使用LGPL认证,允许非共享程序使用这种库。从另一个方面来看,允许非共享程序使用某种库将可以促使大量使用共享软件。例如,GNU C库允许在非共享的软件中使用促使了更多人使用GNU操作系统,以及它的派生GNU/Linux操作系统。

免费IP Core的部分来源

许多非盈利的组织提供免费IP Core,有些CPLD/FPGA的芯片厂商也提供这类共享资源,而芯片厂商提供较多的是针对他们所生产的具体芯片的共享设计。下面介绍两个免费IP Core的非盈利机构。

OpenIPCore工程

该机构旨在推动开放式硬件的发展,其业务既包括提供开放核的平台,也对开放硬件核的权益进行认证,定义设计的方法以及设计接口的标准化。该机构收集经其授权的设计以及免费的开发工具例如gEDA、Savant等,供设计者自由选用。另外为已有的设计如编译器、驱动器、外部电路提供工具、设计和文档的支持。

OpenIPCore工程的基本条款包括:电路核是可以更改的,但必须修改文档记录;不能靠出售核本身来赢利,但是可以出售用核实现的设备,例如基于某些免费核的集成电路、基于某些电路图或版图的电路板,甚至可以是文本模式驱动的图形界面;任何更新都应该备案,并反馈给原设计者;对核的更新、修改或加以完善等成果都应该是共享的;将原封不动的共享核与其他模块结合产生更大的设计,可以在OpenIPCore认证下共享,也可以受其他认证的保护;该网站不保证在实际硬件实现中核的功能和性能。该工程采用OHGPL认证,对基本原创性工作和导出性工作做了明确的定义。该机构不排斥发布人采用其他认证,但要求有明确的声明。

Free-IP 工程

该机构的目标在于利用传统工具发展自由的或成本较低的IP core。由Free-IP 工程提供的IP Core权益不归公共所有而归发布人所有。使用Free-IP核必须遵循以下几点:核的使用是自由的,但是必须遵循所注明的费用项中的信息;不可以出售核,但可以收取复制的费用,也可以对自己添加的有价值的部分收取费用;允许对核修改,但是Free-IP工程不对所做的修改加以认证;对于核的使用没有任何限制,可用于军用、商用、教育等领域。

八位RISC CPU

的比较和分析

核的使用者最关心的是其可靠性。想对所有免费核做出可靠性评价是不可能的,本文通过对两个8位(指数据总线的宽度,指令码为12位)RISC核的对比和分析,给出了在使用免费核时可靠性方面的大体概念。

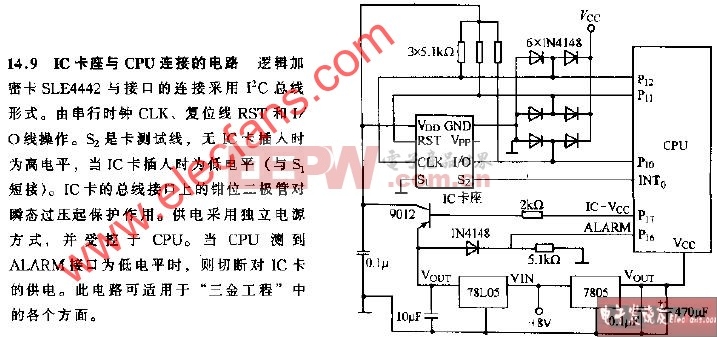

RISC5X是一个用VHDL编写的、与Microchip公司的PIC16C5系列兼容的CPU核,该系列CPU除了程序分支指令外,全部是单周期指令,所以RISC5X在40MHz单一时钟下基本可以达到40MIPS的处理速度。 如采用Xilinx 公司的Virtex-E系列FPGA,该核占用110CLB单元,在E-6上速度可达33MHz,在E-8上可达40MHz。该核提供了VHDL源代码和16进制代码,并且提供了一些不错的免费工具,包括编译器、仿真器和汇编工具(gusim、guasm等)。该核所提供的每一个宏都采用两种结构体写成,一种只适用于Virtex系列目标芯片,另一种是用VHDL的RTL级描述,用户必须根据需要在源程序中作出相应选择。但是存在的缺点是用于定义总线宽度的宏,在第二次使用时,有些综合器并不按要求重复产生第二个硬件模块。一个解决方法是将该宏转换为EDIF格式,每次用到时使用与其对应的EDIF文件名。另一个不足是该核对于双周期指令未做处理,需要用户自己对程序计数器做一定修改。

RISC8是与RISC5X很类似的免费核,与Microchip公司的PIC16C57兼容。该核在ASIC和FPGA层面上都是可综合的,并且已经被使用过。该核提供了CPU、指令译码器、寄存器、累加器、RAM等基本部件,此外还提供了基本的测试向量。在该核的程序包里还可以找到“basic”和“DDS”两个汇编程序,basic用来检测RISC8的指令,DDS则是利用该核的一个应用程序。此外还提供了关于16C57的第三方资源。但是与16C57相比,两者是有明显差别的。表1列出了两者在功能方面的比较。与其他免费核一样,该核也有明显的不足之处,如状态字STATUS中的DC位功能没有完成,以及TRIS不能影响I/O口等。

相比之下,RISC8应该比较成熟,但是由于不能直接使用I/O口,对于有此需要的用户来说,显然尚有很多要做的补充工作。RISC5X的工作相对比较齐全,仅在测试方面稍嫌不足。虽然双周期指令不能直接使用,但是可以用别的指令替代。

从以上比较可以看出,免费核总是有缺陷的,但是工程师可以根据自己的需要找到较为合适的核和使用方法。一般说,一个核往往是由多个模块组成的,有经验的工程师完全可以自行“拼接”比较成熟的模块,成为自己的核。本文的建议如下:

* 在决定选用某个核之前先仔细阅读有关该核的评论(一般可以在核所在的网页上找到),选用那些所存在的缺陷并不影响个人应用的核。例如有些未完成的部分你恰好是不用的;

* 如有多个版本,则宜选用高版本核。高版本都会对核的BUG进行修改,优化后的核通常会有更高的可靠性,例如工作频率的提高等,可以适应更高性能的芯片。

* 如果使用FPGA实现,应尽量采用与发布人一样系列的目标芯片。随核发布的说明文件中通常会指出该核使用何种语言、用何种软件环境调试、曾经综合下载到何种芯片以及硬件调试设备等,在使用时,最好选用同样的芯片和调试环境,而且最好选择同时发布测试向量的核,这样测试起来比较方便。

* 选择时要考虑核使用何种总线标准。如果把不同的IP Core组成一个系统,则需要这些IP Core具有标准的接口。通常情况下,要尽量避免使用三态总线,因为三态总线技术依靠电路延时来避免时序冲突问题,这种对工艺的依赖性,不利于IP Core的复用。免费IP Core通常使用Wishbone总线标准,由于其开放性,拥有了不少的用户。它的特点是同时支持高字节在后(BIG ENDIAN)和低字节在后(LITTLE ENDIAN)的字节编址方式;支持多个主单元;支持点对点、数据流、共享总线以及交叉开关等连接方式。尤其是其交叉方式使得多个主单元可以同时进行数据交换,大大提高了数据吞吐率。

结语

免费IP Core这一丰富的共享资源的有效利用将会带来巨大的价值,开放式硬件的商业应用也是有可能实现的。基于开放式硬件设计的商业模式可以从设计的支持、实现、应用等方面进行,只要仔细研究开放机构的宗旨和规定,使用者就可以发现很多商业应用的渠道。■

参考文献

1 潘松,黄继业. EDA技术实用教程. 科学出版社. 2002

评论