基于DSP的信号采集处理系统

典型的DSP(数字信号处理器)内部采用改进的哈佛结构和流水线技术,可以在单指令周期内完成乘加运算,具有较高的处理能力。一个典型的基于DSP的信号采集处理系统,通常由DSP、A/D转换器、存储器和相应的接口电路组成,大都做成PCI(外设部件互连)接口插卡形式和主控计算机一起工作。各种控制信息通过PCI发送给DSP,采集处理后的结果再通过PCI接口发送回主控计算机。PCI接口部分一般需要采用接口芯片来完成,这样会显著增加系统的设计调试难度,并使成本增加。而选用本身带有PCI接口的DSP处理芯片就可以省去这一部分额外的电路,不但降低了开发难度,也降低了设备成本。TMS320C6205就是这样一种带有PCI接口的DSP芯片,本文重点讨论基于这种芯片的信号采集处理系统的实现方法。

1 TMS320C6205芯片的技术特点

TMS320C6205是基于TMS320C6000平台的高性能DSP,TMS320C6205源自TMS320C6201 B,一种有新的PCI接口且性能提高的DSP芯片。TMS320C6205工作在200 MHz时的最大处理能力达到了1 600 MIPS(百万条指令每秒)。所有TMS320C6000系列DSP芯片在代码上都有兼容性,TMS320C62x定点DSP都基于相同的CPU核心设计,通过指令的并行性获得了较强的处理能力。该系列DSP芯片具有8个处理单元,包括2个乘法器和6个ALU(算术逻辑单元),所有的处理单元都可以并行工作,因此在每一个时钟周期内最多可以同时执行8条指令。

TMS320C6205和TMS320C6201及TMS320C6201B具有高度的兼容性,这几种DSP芯片在以下几个方面完全相同:TMS320C6205的CPU与TMS320C6201B完全相同,因此为TMS320C6201所写的代码可以不加修改地在TMS320C6205上运行;多通道缓冲串口(McBSP)、时钟、中断选择也完全相同;TMS320C6201与TMS320C6205的内部存储空间也相同,都具有64kB的程序和数据存储区。与TMS320C6201相比,TMS320C6205通过升级具有了更强的处理能力,升级后的TMS320C6205和TMS320C6201有以下不同:

a)EMIF(扩展存储器接口总线)做了简单修改,减少了芯片的引脚数。SDRAM(同步DRAM)和SB-SRAM(同步猝发SRAM)在EMIF上共用了相同的控制信号。这两种信号是互斥的,因此在系统中只能在两种类型的存储器中任选一种。

b)为提高DMA(直接存储器访问)的数据吞吐量,4通道的DMA控制器为每一个通道都配备了专用的FIFO,这样就无需对FIFO信号进行仲裁。

c)用PCI模块代替了TMS320C6201B的HPI(主机接口),PCI模块具有高性能的32 bit主/从PCI即插即用功能,支持33 MHz的桌上电脑PCI接口,与PCI本地总线规格2.2版兼容,该接口模块可作为具有33 MHz、32 bit宽度地址数据的PCI主从对象使用,该模块包含配置寄存器、校验生成、校验和系统错误检测和报告(PERR#,SERR#)以及电源管理能力。

d)具备4线EEPROM串行接口,这样,PCI的控制空间寄存器就可以从外部的串行EEPROM加载配置,PCI模块无需DSP的干涉就可以实现自动初始化。

e)TMS320C6205的PLL有x1、x4、x6、x7、x8、x9、x10和x11等模式,这些模式可以通过CLKMODE0引脚和EMIF数据引脚的上推和下拉电阻来选择。

f)TMS320C6205使用15C05(0.15μm)处理技术,通过电池处理技术提供更低的核电压和功耗。

g)用上推和下拉电阻实现了自举模式配置。

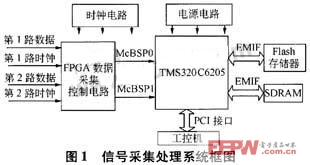

2 信号采集处理系统硬件设计

该系统硬件部分主要由DSP、FPGA(现场可编程门阵列)和存储器构成,具体的硬件结构如图1所示。

评论