IC验证进入“验证3.0时代”

当前,IC设计的验证环节已成为IC设计的瓶颈,一家企业的验证水平直接影响了新产品的推出速度;而且验证方法也到了瓶颈,需要新方法迅速提升验证效率。

本文引用地址:https://www.eepw.com.cn/article/247118.htm近日,Mentor Graphics公司董事长兼CEO Walden C. Rhines在美国总部称,IC验证正进入“验证3.0时代,即系统时代,软硬件协同验证。

原因是当今SoC更复杂,诸如系统中含有多个嵌入式内核,异构处理器,复杂的内部互联,共享存储器,片上芯片(NoC)及多级缓存。

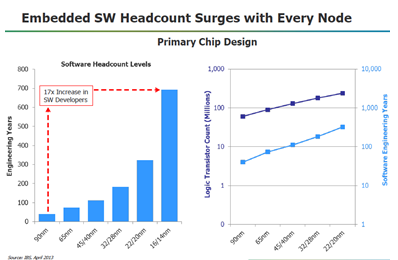

与此同时,随着工艺制程节点的不断演进,对嵌入式软件工程师的需求量急剧上升。

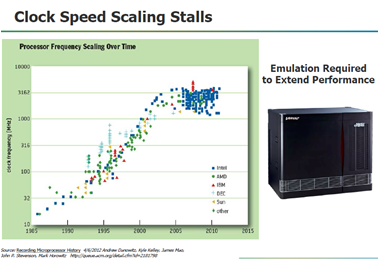

但芯片的时钟速率徘徊不前,因此需要硬件仿真器扩展性能。

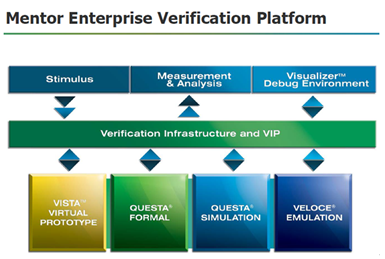

而且很多公司的SoC设计团队分布全球各地,因此需要企业级的解决方案,有统一的调试、统一的验证IP、统一的用户接口、统一的testbench仿真,统一的断言,统一的覆盖。

所有验证都在统一环境下,这个环境里有软件仿真、正规的引擎和硬件仿真。支持硬件和软件调试:从OS boot和设备驱动器,到目标外围。

为此,Mentor发布了企业验证平台(EVP)。该平台将先进的验证解决方案Questa®、全球硬件仿真资源分配技术Veloce® OS3和强大的调试环境Visualizer™融合在一起,形成一个全球范围内可用的高性能资源数据中心。Mentor EVP的全球资源管理特性可以支持公司世界各地的项目团队,最大程度地提高用户的生产率和总的验证投资回报率。Mentor EVP可将仿真性能和生产率提高400~10,000倍。

评论