Leon2处理器IP核技术(二)

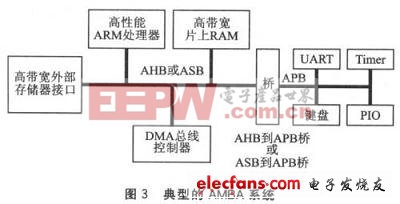

AMBA(Advanced Microntroller Bus Architecture)规范,是一种已制定的、开放的规范,充当着SoC设计的架构,正迅速成为SoC和IP库开发事实上的标准,为高性能嵌入式微控制器设计定义了一种片上通信标准.AMBA规范中定义了三种不同的总线,即AHB、ASB和APBAHB是为高性能、高时钟频率的系统模块提供的,担任着高性能系统的背板总线、支持多处理器、片上各种存储器和片外外部存储器接口连接到低功耗辅助宏单元。ASB也是为高性能系统模块提供,当AHB的高性能特点无需要时,就可以用ASB来代替;它也支持多处理器、片上各种存储器和片外外部存储器接口连接到低功耗辅助宏单元。APB是为低功耗的外围设备提供的,它优化到为最小功耗和减小接口的复杂性来支持辅助功能。

图3是AMBA总线微控制器的典型结构。它含有一套高性能的背板总线,AHB或ASB;它能支撑外部存储器带宽,在这套总线挂接着CPU、片上存储器和其他DMA设备。通过一个桥接器,可以把AHB和APB总线连接起来。APB上面连接着大多数的辅助设备,如UART、定时器、PIO等。

2.3 容错问题

为了适用于航空航天的高可靠性应用,Leon2采用多层次的容错策略;奇偶校验、TMR(三模冗余)寄存器、片上EDAC(检错和纠错)、流水线重启、强迫Cache不命中等.尽管现在几乎所有CPU都有一些常规的容错措施,如奇偶校验、流水线重启等,像IBM S/390 G5还采用了写阶段以前的全部流水线复制技术.IntelItanium采用的混合ECC和校验编码等技术;但远没有Leon2那样,采用如此全面的容错措施。

Leon2将时序(存储)单元的状态翻转作为数字容错的主要内容,根据时序逻辑的不同特点和性质,采用了不同的容错技术和手段.

①Cache的容错。大的Cache对高性能CPU来说是至关重要的,而且位于处理器的关键(时间)通路上。为了减少复杂性和时间开销,错误检测的方法采用2位的奇偶校验位,l位用作奇校验,l位偶校验,因此可以检查所有的错误情况,在读Cache的同时进行校验。当校验出错误,强制Cache丢失,并从外部存储去获取数据。

②处理器寄存器文件的错误保护。寄存器文件是处理器内部的寄存器堆,内部的寄存器对于指令的运行速度和用户程序设计的灵活程度都是很重要的。内部寄存器的使用频率很大,其状态的正确性是也很关键。Leon2采用1、2奇偶校验位和(32.7)BCH校验和进行容错。

③触发器的错误保护。处理器的2500个触发器均采用三模冗余的方式进行容错,通过表决器来决出正确的输出。

④外部存储器的错误保护。采用挂上的EDAC单元实现。EDAC:采用标准的(32.7)BCH码,每32位字可纠正1位错误和检测2位错误。

⑤主检测模式。是指两个相同的处理器同时并行执行相同的指令,只让其中的主模式处理器输出结果,不让检测模式的处理器输出结果。在内部,将检测模式处理器的输出同主模式处理器输出进行比较,以检查错误是否存在。这种工作模式,可以应用于要求更高可靠性的情况。

⑥在软件上,还要考虑Cache的清洗问题。因为上面介绍的五种方法,只有在对相应的单元进行访问时才进行错误检查。如果存储单元的数据不常使用,这些单元的错误会逐渐增加,因此必须使用一些软件的方法来实现。

2.4 编码风格

评论