三大先进制程代工厂的路线图

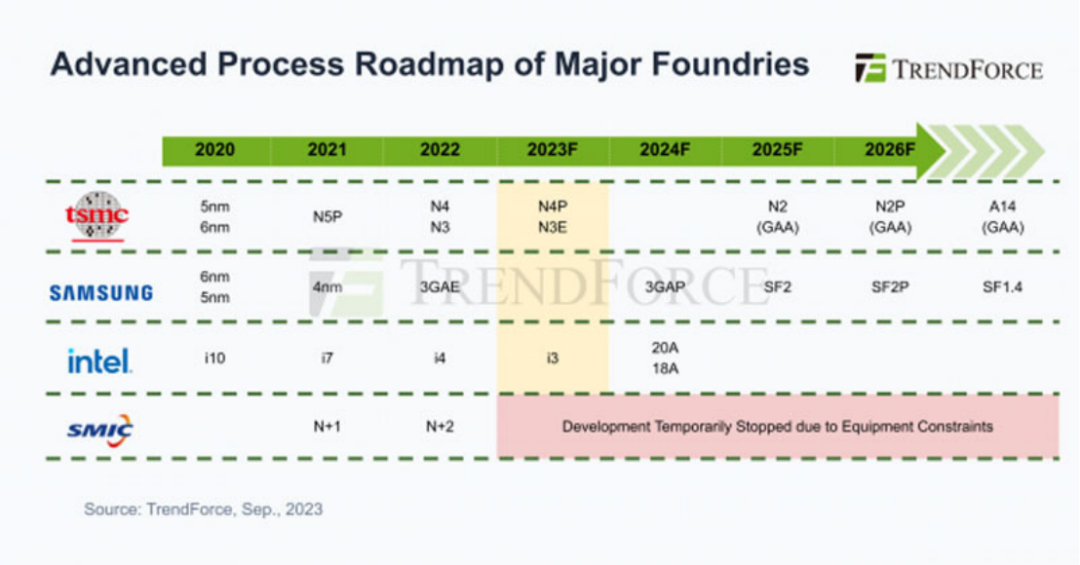

据集邦咨询报道,台积电、三星、英特尔等尖端制程代工厂纷纷发布 2nm 及以上制程路线图,凸显下一代 GAA 技术领先地位的开发竞争加速。

本文引用地址:https://www.eepw.com.cn/article/202310/451774.htm

大型晶圆厂的前沿工艺路线图。请注意,这是 TrendForce 根据各公司公布的计划创建的,不一定完全如图所示(来源:TrendForce,截至 2023 年 9 月)

台积电将于 2025 年在宝山工厂开始量产 2nm 工艺

关于产业龙头台积电,集邦科技将于 2024 年第二季开始在中国台湾新竹科学园区宝山地区(新竹县宝山乡)的工厂安装量产 2 纳米(N2)制程的制造设备。计划于 2025 年第四季度开始量产,月产量约为 30,000 片晶圆(12 英寸晶圆)。此外,新指定为 2nm 量产基地的高雄工厂,将于 2026 年(即 N2 开始量产一年后)开始量产 HPC 用背面供电技术的「N2P」。顺便说一句,与传统技术相比,背面供电技术据称可提高速度 10% 至 12%,逻辑密度提高 10% 至 15%。

台积电似乎也计划在中国台湾北部(桃园)的龙潭科学园区建立一座 2 纳米及以上的尖端半导体工厂(也许是为了增加 2 纳米或 1.4 纳米的产量),但这一计划遭到了来自当地居民的反对。10 月 17 日,台湾多家媒体同时报道。新工厂原定建在台湾政府科学园区管理局为科技园区第三期扩建而征用的土地上,但许多当地居民被要求离开,以便为工厂扩建让路。由于遭到公众强烈反对,这个想法不得不被放弃。细节尚未透露,但暂时计划在两家工厂量产 2nm 产品,放弃本次拿地不会影响公司 2nm 工艺产品的生产。

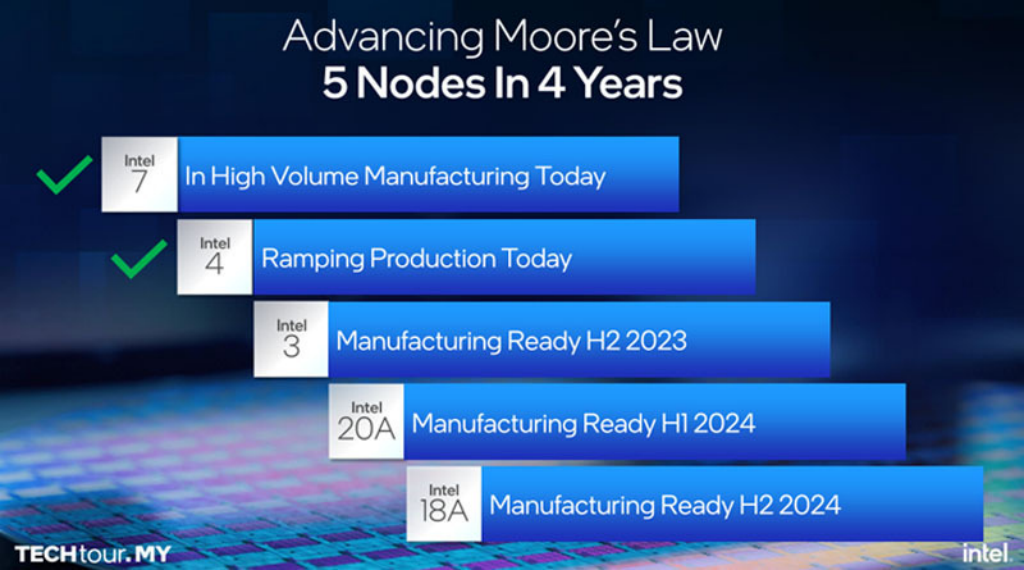

英特尔计划在四年内实现五个技术节点

另一方面,英特尔正在从 FinFET 快速发展到基于环栅 (GAA) FET 的 MBCFET 和 BSPDN(背面供电网络)技术。该公司制定了「四年内实现五个技术节点」的快速小型化目标,并计划在 2024 年赶上并超越其他公司。英特尔计划于 2024 年上半年开始生产采用基于 GAA 技术的 RibbonFET 晶体管架构的英特尔 20A 工艺,并宣布计划将生产转移到其衍生的英特尔 18A 工艺。

英特尔 4 年内实现 5 个技术节点的路线图(来源:英特尔,2023 年 8 月)

该公司目前正在其爱尔兰工厂量产 Intel 4 工艺,但尚不清楚该公司是否拥有足够的 EUV 曝光设备,该公司是否能够按计划维持其路线图还有待观察。此外,该公司计划领先于其他公司推出针对 2 纳米左右制程的高 NA(NA=0.55)的 EUV 曝光设备,但高 NA EUV 曝光设备也已如期推出,目前尚不清楚。它将投入实际使用。

三星从 3nm 开始采用 GAA 将是未来的试金石

三星的代工业务先于其他公司采用了 3nm 工艺的 GAA 架构,但似乎正面临良率低等问题。该公司计划于 2025 年开始采用 2nm 工艺量产,并计划于 2027 年开始采用 1.4nm 工艺量产。台积电和英特尔计划从 2nm 工艺开始采用 GAA 架构,但较早引入 GAA 的三星如果能利用其在 2nm 的经验,将获得先发优势,提供比其他公司更高的良率并赢得市场

此外,主要受到美国对中国半导体法规影响的中芯国际已暂停其小型化计划。这是因为 ASML 的 EUV 光刻设备尚未可用,但他们似乎已经利用现有的 ArF 浸没式光刻设备实现了使用多重图案化的 7nm 工艺,并且也有传言要达到 5nm 工艺。此外,日本 Rapidus 计划在合作伙伴 IBM 和 imec 的合作下,于 2027 年底在日本开始量产 2nm 工艺,但未来的路线图仍在进行中,直到 2nm 工艺推出为止。可见,因为它不可见。此外,台积电和三星还制定了 2027 年将 1.4 纳米作为尖端工艺应用于量产的路线图。

中国大陆成熟制程产能观察

据 TrendForce 集邦咨询统计,2023~2027 年全球晶圆代工成熟制程(28nm 及以上)及先进制程(16nm 及以下)产能比重大约维持在 7:3。中国大陆由于致力推动本土化生产等政策与补贴,扩产进度最为积极,预估中国大陆成熟制程产能占比将从今年的 29%,成长至 2027 年的 33%,其中以中芯国际(SMIC)、华虹集团(HuaHong Group)、合肥晶合集成(Nexchip)扩产最为积极。

Driver IC 方面,主要采用 HV(High Voltage)特殊工艺,各家业者近期聚焦 40/28nm HV 制程开发,而目前市场制程技术较领先的业者是联电(UMC),其次是格芯(GlobalFoundries)。不过,中芯国际 28HV、合肥晶合集成 40HV 将先后于今年第四季、明年下半年进入量产阶段,并与其他晶圆代工业者的技术差距逐渐缩小,尤其制程能力与产能相当的竞争者如力积电(PSMC),或暂无十二英寸厂的世界先进(Vanguard)、东部高科(DBHitek)短期内将首当其冲;对联电、格芯中长期来看也将造成影响。

CIS/ISP 方面,3D CIS 结构包含逻辑层 ISP 与 CIS 感光层,主流制程大致以 45/40nm 为分水岭,逻辑层 ISP 制程将持续往更先进节点发展;CIS 感光层与 FSI/BSI CIS 则以 65/55nm 及以上为主流。目前技术领先业者以台积电(TSMC)、联电、三星(Samsung)为主,但中芯国际、合肥晶合集成紧追其后,除持续追赶制程差距,产能也受惠中国智能手机品牌 OPPO、Vivo、小米(Xiaomi)等支撑,加上陆系 CIS 业者 OmniVision、Galaxycore 与 SmartSens 响应政府政策,陆续将订单移回中国大陆进行投产支撑。

Power Discrete(功率元件)方面,主要涵盖 MOSFET 与 IGBT 两种产品,世界先进、HHGrace 深耕 Power Discrete 制程已久,制程平台及车规验证覆盖完整性皆较其他同业更高。而受惠于大陆电动车补贴政策以及铺设太阳能相关基础建设,陆系晶圆代工业者据此获得更多切入机会,包含主流代工厂 HHGrace、中芯国际、合肥晶合集成、CanSemi 在内的业者,加上本土小型的 Power Discrete IDM、晶圆厂如 GTA 及 CRMicro 等均加入 Power Discrete 竞争行列。若大陆产能同时大量开出,将加剧全球 Power Discrete 代工竞争压力。

整体而言,中国大陆透过积极招揽海外及境内 IC 设计业者投产或研发新品,目的为提高本土化生产的比例,但大幅扩产的结果可能造成全球成熟制程产能过剩,且随之而来的将会是价格战。TrendForce 集邦咨询认为,中国大陆成熟制程产能陆续开出,针对 Driver IC、CIS/ISP 与 Power discrete 等本土化生产趋势将日渐明确,具备相似制程平台及产能的二、三线晶圆代工业者可能面临客户流失风险与价格压力,技术进展和良率将是后续巩固产能的决胜点。

评论