英诺达发布DFT静态验证工具,提高IC设计质量及可靠性

英诺达(成都)电子科技有限公司发布了自主研发的静态验证EDA工具EnAltius®昂屹® DFT Checker,该工具可以在设计的早期阶段发现与DFT相关的问题或设计缺陷。

本文引用地址:https://www.eepw.com.cn/article/202309/450520.htm随着芯片规模和复杂度的提升,芯片各种逻辑和电气功能验证的要求越来越高,多种RTL编码风格、以及存在于电路设计中的结构性和功能性问题更容易成为设计上的缺陷,导致设计不断修改,甚至造成流片失败的风险。此外,设计重用性和IP的高集成度对模块设计在正确性和一致性方面提出了更严格的要求,以提高IP集成的可靠性和成功率。

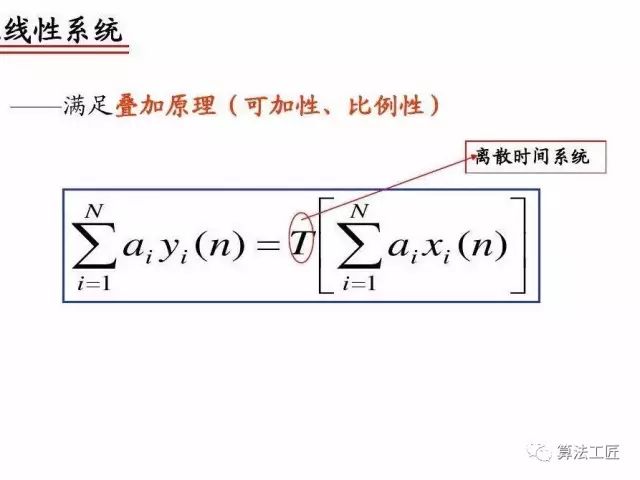

上述芯片设计的挑战可以通过传统的基于仿真的动态验证工具和技术得到一定程度的解决,然而,现代的SoC设计需要强大的静态验证技术作为补充,以缩短设计时间并提高首次流片的成功率。更为难得的是这种技术可在设计的早期阶段发现设计缺陷,从而避免设计团队大量无效时间和精力的投入。

英诺达是国内第一家专注于开发以IC设计代码分析和规则检查为基础的静态验证工具的EDA企业,可提供全面的用于分析、查错和修复的EDA解决方案,可在设计的早期阶段(RTL阶段或逻辑综合阶段)对结构性、功能性和电气性等电路问题进行深入的分析。继EnFortius®凝锋®系列两款低功耗静态验证工具发布之后,英诺达此次发布的昂屹®DFT Checker静态检查工具,可以对RTL或网表设计进行结构性和功能性分析,在设计早期阶段提高IC设计的质量。

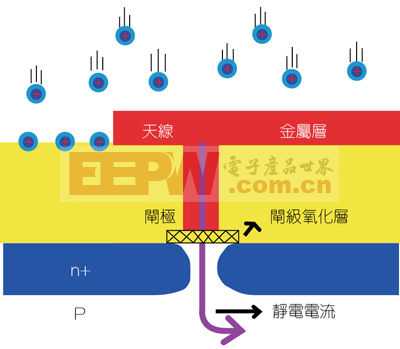

DFT(可测试性设计,Design-For-Test)是设计收敛的关键一环,通过在设计上增加逻辑,使芯片的测试更高效和更容易,此外,还可以提高良品率、降低成本。因此,确保芯片设计符合DFT设计规则,提高测试覆盖率是所有设计团队都要面对和解决的问题。当前,DFT测试覆盖率通常要求达到99%以上,因为任何漏掉的测试向量都可能导致芯片在实际应用中出现故障。而在设计后期增加DFT逻辑会对性能、功耗和面积产生较大影响,会导致设计迭代甚至重新设计。所以,在设计的早期阶段提高代码的质量至关重要。

昂屹®DFT Checker基于英诺达首款EDA工具凝锋® LPC的底层架构和先进算法,该款工具可提供早期RTL可测试性分析功能,同时也支持传统的基于网表的流程。除了对可测试性问题的早期分析之外,该工具还可以缩短完成DFT设计的时间,并确保设计在可测试性部分达到交付标准。

该款工具涵盖了全面的结构、功能和电路规则检查,可有效提高测试覆盖率。基于先进的SoC设计规则和方法学,昂屹®DFT Checker可验证芯片在不同模式下所有连线的正确性、完整性和集成性。此外,为了提高设计效率,该工具提供以目标为导向的报错信息,帮助设计师快速过滤、定位和调试设计上的问题。对此,益昂半导体副总范学锋表示:“DFT设计是IC设计不可缺少的一环,英诺达DFT Checker可以帮助设计师在设计的早期阶段发现并更正对DFT不友好的设计,使得后期的DFT综合与实现更快速收敛,从而提高设计效率。”

英诺达副总经理熊文表示:“在IC设计早期应用静态验证工具可以帮助IC工程师进行高效的设计验证及关键性的优化,英诺达已发布了两款低功耗领域的静态验证工具,在超大规模电路设计上可以快速完成低功耗设计的检查及功耗的分析与验证。除低功耗设计领域之外,静态验证可应用的领域还有很多,昂屹®DFT Checker就是我们的又一突破创新产品。英诺达将把握这一优势,不断开拓,继续为国产EDA静态验证工具补齐短板,为IC工程师的设计效率和芯片良率保驾护航。”

评论