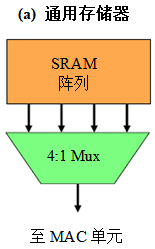

Zeno开发特殊SRAM 可提升MOS结构效能

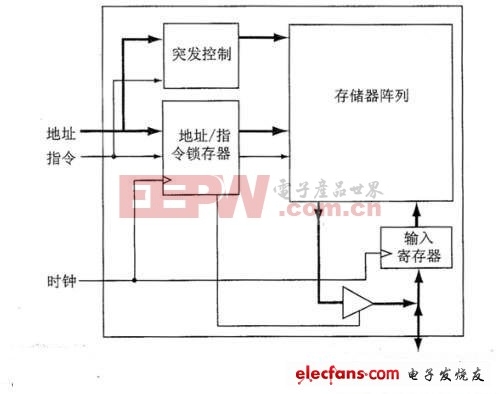

Zeno Semiconductor日前开发出将最小静态随机存取存储器(SRAM)纳入单一MOS电晶体技术,不仅其采用记忆单元(bit-cell)数量变多,存取时间也可大幅缩短4成。

本文引用地址:https://www.eepw.com.cn/article/201601/285239.htm据EE Times网站报导,Zeno在国际电子零组件会议(International Electron Devices Meeting)上展示这项新技术。Zeno执行董事长Zvi Or-Bach表示,该技术之所以让N型MOS电晶体做为稳定SRAM,主要是透过采用2个本质双极N-P-N型电晶体所赐。

该技术看似为3个电晶体记忆单元,但由于是采用本质元件,具备开放闸极与共集电极的双极N-P-N型电晶体可被视为虚拟电晶体。换句话说,并未占据多余芯片空间,为一善用单一MOS电晶体架构的范例。

另外,其记忆单元大小也只有0.025平方微米,比一般0.127微米还小。

Zeno 28奈米SRAM记忆单元大小也比三星电子(Samsung Electronics)10奈米FinFET SRAM记忆单元小37%,不管采用3D FinFET或全空乏绝缘上覆矽(FD-SOI)平面晶圆,即使在先进制程仍可维持其大小水准。

Zeno也希望透过2款电晶体满足利基市场需求,包括拥有5倍记忆单元的单一电晶体以及增加1个存取电晶体成为双电晶体记忆单元,来降低漏电流与存取时间达4成的电晶体,同时其记忆单元仍多出3倍。

该公司执行长Yuniarto Widjaja指出,单电晶体Bi-SRAM主要锁定对价格敏感及强调低功耗的市场,例如物联网(IoT),后者双电晶体则瞄准网路或高效能运算(HPC)等市场。其大小技术优势可在FinFET或FD-SOI等先进制程或较早制程上得以发挥,Zeno也针对逻辑与存储器芯片推出架构。

评论指出,一旦Zeno透过双功能数位电晶体将其他元件缩小尺寸,将等于可避免继续透过采取更先进制程微缩必要性。有别于一般公司采取持续微缩芯片做法以便容纳更多电晶体,Zeno则是开发更少与更小电晶体技术来达到同样效果。

Zeno技术优势并非只有采用本质双极电晶体,同时也省略会占用芯片面积的电容器等元件。换句话说,虽采用标准CMOS制程,但可达到元件小5倍以及存取时间更快40%的结果。

Zeno架构与制程目前拥有50件以上专利,该公司则透过授权IP方式向其他公司开放,不过并未透露其客户名单。

评论