ADSP TS201链路口通信的FPGA实现

O 引 言

随着电子技术的飞速发展,在实际应用中数据高速传输有着越来越高的要求,链路口为数据传送提供了高速、独立的通信机制,得到广泛应用。AD公司生产的TS201 DSP就具备这种端口。为了使不具备此接口的器件同样也能通过链路口与TS201进行高速通信,引入FPGA进行设计。

FPGA器件因其集成度高、功能强大、现场可编程等优点被广泛应用于各种场合。通过在FPGA上参照链路口通信协议编写VHDL程序,完成数据传送方式的转换,实现此接口与其他设备通信,以满足系统的高速通信要求。

本文设计了一种基于Xilinx公司Virtex4系列的FPGA的128位并行数据与ADSP TS201的链路口通信方式。

l ADSP TS20l链路口协议

ADSP TS201有4个链路口均采用LVDS(Low

Voltage Differential Signaling)电路,每个链路口都是由4位双向差分数据线和另外3个控制信号构成。接收控制信号包括:Lxclkinp/n,Lxacko,Lxbcmpi;发送控制信号包括:Lxclkoutp/n,Lxacki和Lxbcmpo。其中,Lxclkoutp/n和Lxclkinp/n用于描述输出或输入信号的时钟,Lxacko和Lxacki则表示接收端发出的信号和发送端接收的信号表明是否可以继续发送,Lxbcmpi和Lxbcmpo说明块传输已经完成。链路口每个方向(Rx或Tx)均可通过1位或4位数据总线通信,发送端发送数据到外部设备,接收通端从外部设备获取数据。这里主要讨论4位数据总线通信模式的具体实现。

在链路口通讯协议的时序上采用一些通用规则,具体规则如下:

①第一个数据(1位或4位)必须在链路口时钟(Lxclkoutp)的第一个上升沿发送。

②后一个数据(1位或4位)必须在链路口时钟(Lxclkoutp)最后一个下降沿发送。

③当链路口停止收发后Lxclkoutp被置为低。

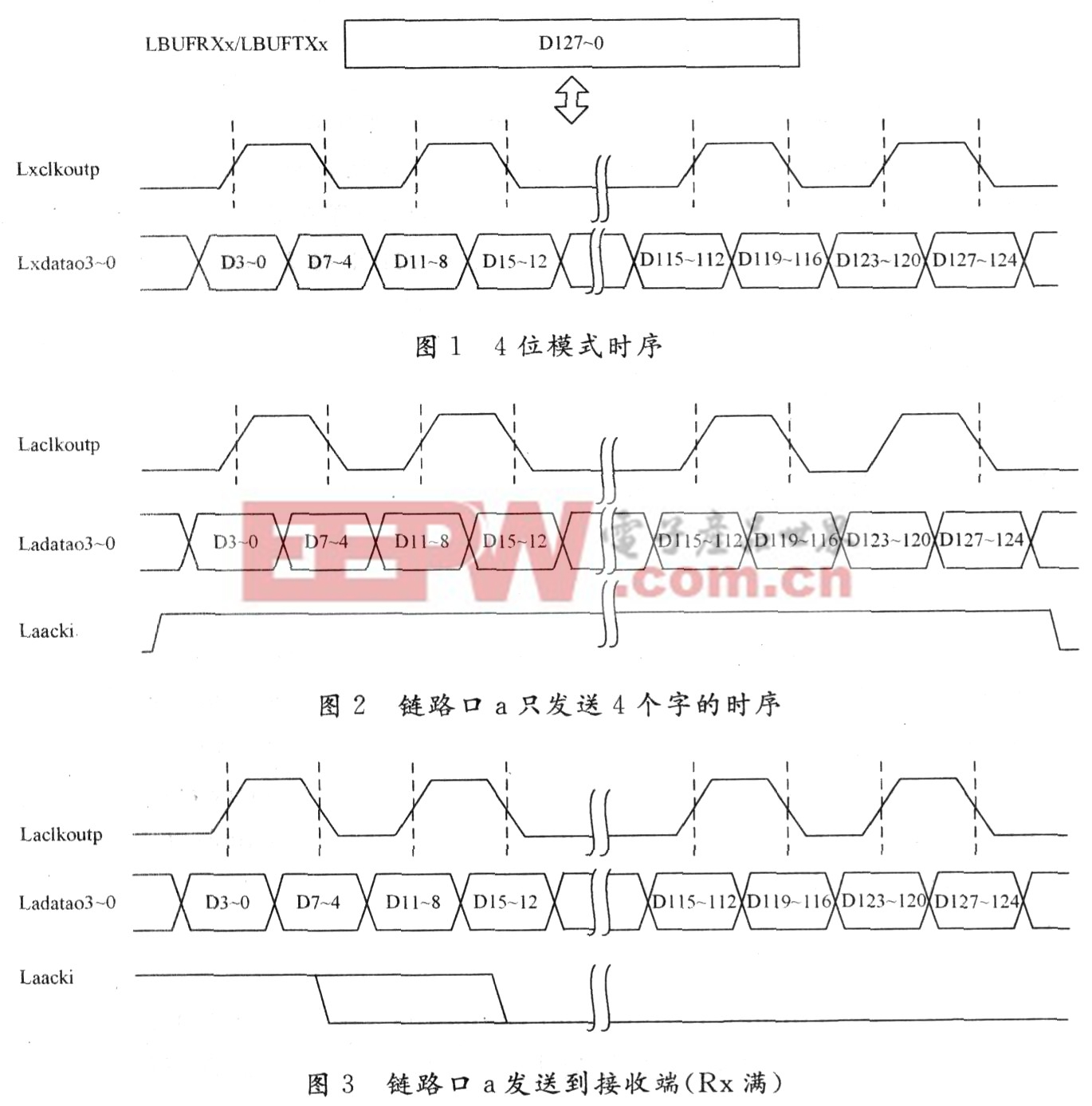

④每次至少传送4个字(128位)。传送需要用16个名车略口周期,如图1所示。

当Lxacki被置为高,即接收缓冲是空的,发送通道被初始化,发送端可以继续发送数据。如图2所示,第一个数据在第一个Lxclkoutp上升沿有效,最后一个数据在最后一个链路口时钟下降沿之前发送。当链路口停止时Lxclkoutp被置为低。

图3表示当Lxacki被置为低时,说明接收端没有准备好接收更多数据的情况。此时若仍有数据传送,则会造成数据的丢失。

当发送数据长度可变时发送方用Lxbcmpo信号通告接收数据块传输已完成。Lxbcmpo与接收端的Lxbcmpi输入信号连接,当接收端识别该信息,就通知DMA通道数据块传送完毕。

Lxbcmpo信号通过在块的最后4个字传输的第一个Lxclkout上升沿变低,指示块传输完成。而在同一4个字的最后一个Lxclkout下降沿置位。若LTCTLx寄存器中的TBCMPE位被清除或当链路口传输由处理器核执行,Lxbcmpo无效。

评论