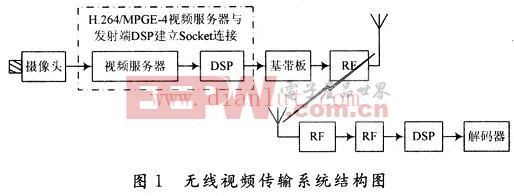

ADSP TS201链路口通信的FPGA实现

子模块fast控制模块是由clk,clknot,clkd2和clkd2not四个时钟组合生成,产生muxO和muxl两个控制信号。当mux0=0时Datainn(3:O)输出到DataO,反之,当muxO=1时Datainn(11:8)输出到Data0;同样,当muxl=0时Datainn(7:4)输出到Datal,反之,当muxl=0时,Datainn(15:12)输出到Datal。

为了提高速度,保证高频率下程序的稳定性,使用rloc命令,通过对。fast模块各个触发器属性描述及对底层基本逻辑单元的相对位置进行约束,使得同一组数据的触发器放置相对集中,从而减少了由于时钟信号在布局布线中产生延迟使得数据建立时间不足而引起的不定态。

3 实现与仿真

ModelSim是一个独立的仿真工具,在Xilinx公司的ISE集成开发环境中给ModelSim仿真软件预留了接口,通过这个接口可以从ISE集成工具中直接启动ModelSim工具进行仿真。由于厂家的推广,ModelSim得到了广泛的应用。

仿真也可分为功能仿真和时序仿真等3大类型。由于特殊底层元件的使用,需要一些器件库模型的支持。而综合后门级功能仿真以及实现后时序仿真都需要厂家器件库的支持。

因此,在使用ModelSim 6.2进行功能级仿真和布局布线后仿真时,应根据需要提前对Xilinx的UN ISIM,XmnxCoreLib,SIMPRIM,SmartModel库进行编译。其中,UNISIM库包含了Xilinx公司全部的标准元件;XilinxCoreLib则包含了使用Xilinx CoreGenerator工具生成的IP的仿真模型;SIMPRIM库用来做时序仿真或者门及功能仿真;SmartModel库用来模拟复杂的FPGA设计。

首先按如下步骤完成对XX的编译:

(1)将ModelSim根目录下的modelsim.ini文件的属性设置为存档;

(2)在ModelSim的命令窗口中输入命令:“compxlib―s mti_se-arch all―l vhdl―w―lib all”;

(3)将ModelSim.ini文件的属性重新设置为只读。

环境建立好以后,首先对程序进行功能级仿真,验证功能是否达到要求;功能仿真正确后再进行布局布线后仿真,根据布局布线仿真的情况再对程序进行分析,调整或者修改原先的设计,以满足设计要求。

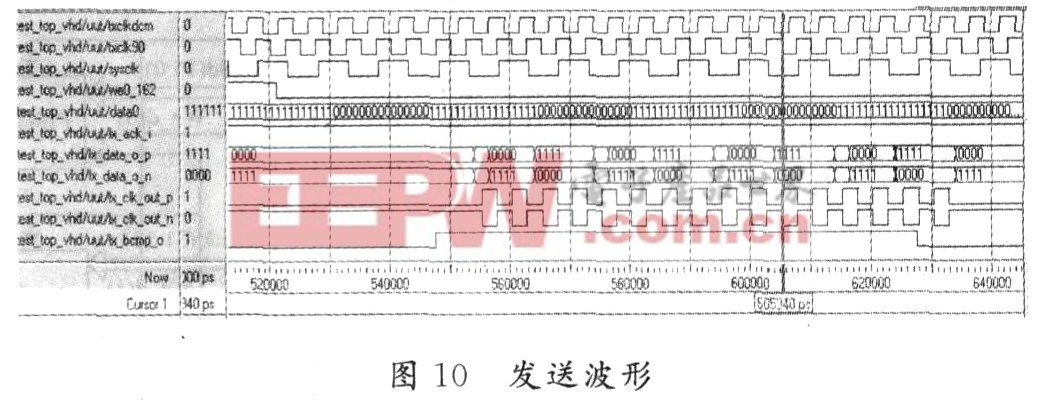

发送:此波形显示将128位数据Data0转换成链路口的传送协议送出,如图10所示。

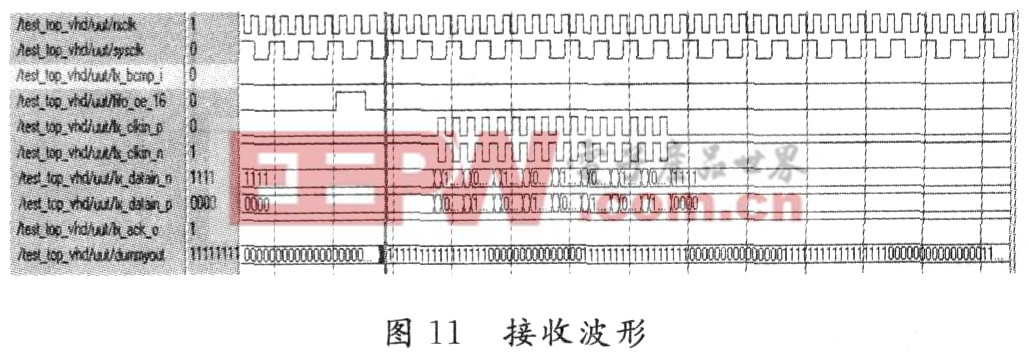

接收:此波形表示有TS201链路口接收到一组数据,当FIFO_oe(即FIFO读信号)为高时将数据并行送出,如图11所示。

结 语

本文介绍了一种利用VHDL语言在FPGA上实现链路口通信的方法,实现FPGA与ADSP TS201之间的高速链路口通信。设计最终能达到的接收链路时钟频率为500 MHz,发送链路时钟频率为400 MHz,充分发挥了链路口通信的速度优势。也使得ADSPTS201通过具有此功能的FPGA与其他并行接口器件或设备进行高速通信成为可能。

评论