ADSP TS201链路口通信的FPGA实现

2 模块建立与优化

ADSP TS201的链路口采用的是独立的发送和接收通道,因此对应的FPGA也需要采用不同的接收电路和发送电路。

无论是接收还是发送均由两部分组成:接收/发送缓冲和接收/发送模块。接收模块主要是用于接口和数据的拆包处理,发送模块是用于数据接收和打包处理。接收/发送缓冲则是用来分别配合接收/发送模块进行数据缓冲,并实现数据传输功能。

2.1 接收电路

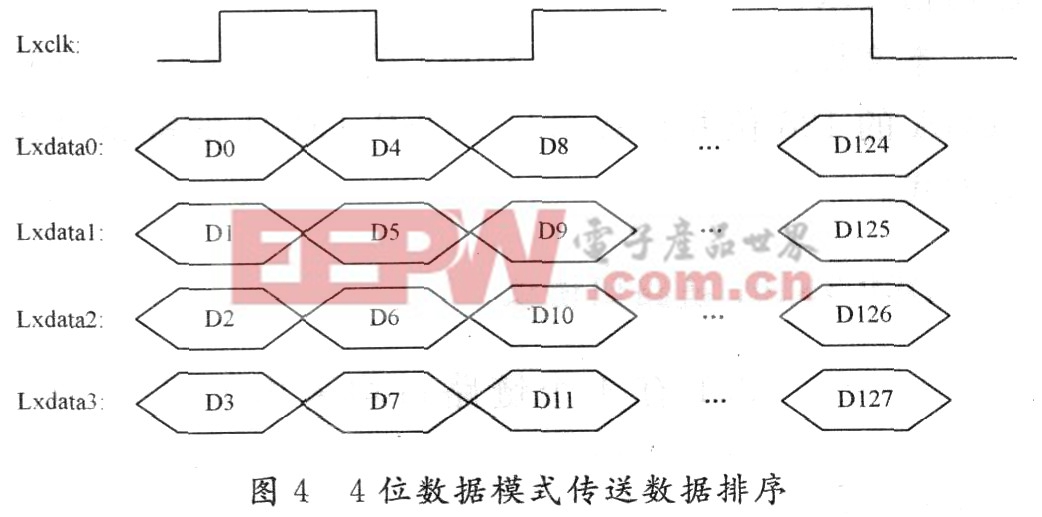

接收模块:接收到由链路口4位数据总线送出的数据差分信号Lxdatap/n和控制差分信号Lxclk p/n以后不能直接拆包处理,需要将原来的差分信号转换成完整信号、Lxdata和Lxclk,才可进入双倍数据速率器(DDR)寄存,此寄存器由时钟信号clkin(与Lxclk同频率)控制。由于是4位数据总线同时串行传送数据,其具体的数据排序如图4所示。本文引用地址:http://www.eepw.com.cn/article/192061.htm

可见,每一路传送的数据均不是连续的,且都按模4余数分配。为了方便数据并行送出,需要将数据进行拆包整理。每个clkin周期收到8位数据,将此按位号由大到小的顺序整理,并放入mid(7:O)中。其间增加一级触发器作为缓冲。

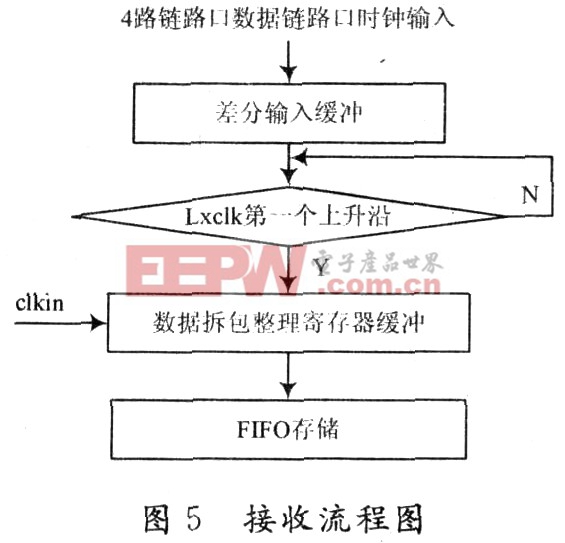

接收缓冲:此部分主要由状态机和FIFO构成,其中状态机主要控制FIFO写命令的产生,由链路口时钟Lxclk和时钟信号clkin共同产生,即当Lxclk产生第一个上升沿时计数器开始计数从O~15,每次计数就会将相应的FIFO写许可we d置为有效。将128位数据每8位为一组,分别送入16个8位F1FO中,由外部的FIFO_oe读信号和sysclk时钟信号控制128位数据并行读出。即将FIFO_oe信号同时接到16个FIFO上,当FIFO_oe有效时,从16个FIFO中同时读出数据。并根据FIFO存储状态发送Lxacko信号和fuiIflag信号,若FIF0不满则将Lxacko信号置为1(高有效)允许发送端继续通过链路口发送数据;否则Lxacko置为O。

其中,FIFO 8由Core generator直接生成,是异步8位先进先出存储器。下面涉及的FIFO 16,FIFO 32均这样生成。接收(Rx)流程图如图5所示。

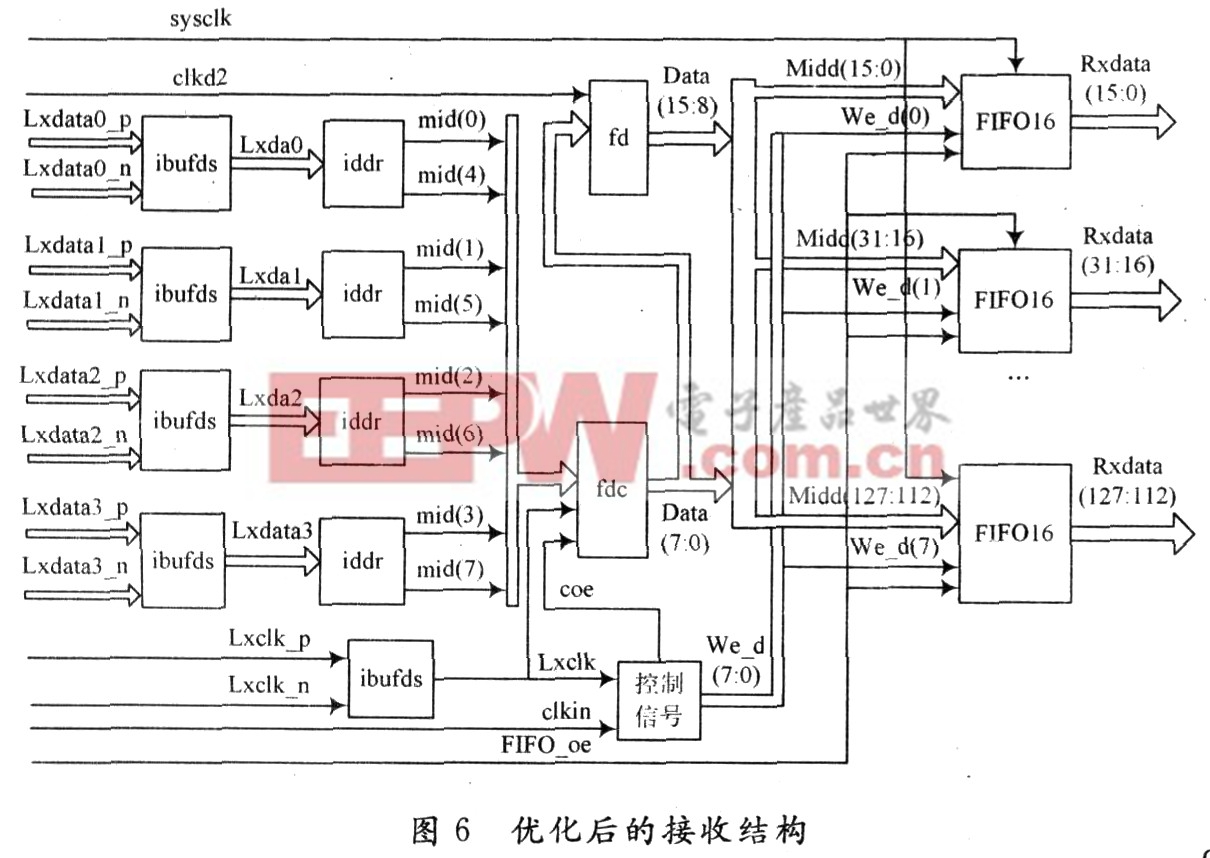

综合后此电路的主时钟Clkin频率最快可达到368 MHz。由于一个FIFO 8就占用了一个18 Kb的嵌入式FIFO资源,而16个FIFO就占据了16个块的资源,这不仅造成了资源的浪费,还增加了布局布线所需要的时间。因此,为了优化结构,增加一级寄存器,扩展数据的位数,使得数据在未进入FIFO前就已得到处理,由原来的8位数据mid连成16位数据Data,再送入16位的FIFO 16中。优化后,FIFO 16的使用率由原来的22%减少到11%,大大减少了线上延迟。综合此电路的主时钟clkin频率最高可实现500 MHz。具体结构如图6所示。

2.2 发送电路

评论